# TEXAS INSTRUMENTS

Data sheet acquired from Harris Semiconductor SCHS062

# CMOS Binary Rate Multiplier

High-Voltage Types (20-Volt Rating)

■ CD4089B is a low-power 4-bit digital rate multiplier that provides an output pulse rate that is the clock-input-pulse rate multiplied by 1/16 times the binary input. For example, when the binary input number is 13, there will be 13 output pulses for every 16 input pulses. This device may be used in conjunction with an up/down counter and control logic used to perform arithmetic operations (adds, subtract, divide, raise to a power), solve algebraic and differential equations, generate natural logarithms and trigometric functions, A/D and D/A conversions, and frequency division.

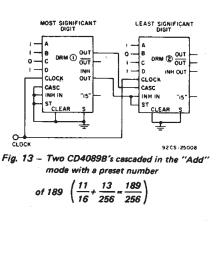

For words of more than 4 bits, CD40898 devices may be cascaded in two different modes: an Add mode and a Multiply mode (see Figs.14 and 15). In the Add mode some of the gaps left by the more significant unit at the count of 15 are filled in by the less significant units. For example, when two units are cascaded in the Add mode and programmed to 11 and 13, respectively, the more significant unit will have 11 output pulses for every 16 input pulses and the other unit will have 13 output pulses for every 256 input pulses for a total of

<u>11 13 189</u> 16 256 256

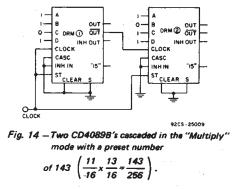

In the Multiply mode the fraction programmed into the first rate multiplier is multiplied by the fraction programmed into the second multiplier. Thus the output rate will be 11, 13, 143

16 16 256

### Features:

- Cascadable in multiples of 4-bits

- Set to "15" input and "15" detect output

- = 100% tested for guescent current at 20 V

- = 5-V, 10-V, and 15-V parametric ratings

- Standardized, symmetrical output characteristics

- Maximum input current of 1 μA at 18 V over full package-temperature range; 100 nA at 18 V and 25°C

- Noise margin (full package-temperature range) =

1 V at V<sub>DD</sub> = 5 V 2 V at V<sub>DD</sub> = 10 V 2.5 V at V<sub>DD</sub> = 15 V

Meets all requirements of JEDEC Tentative Standard No. 138, "Standard Specifications for Description of 'B' Series CMOS Devices"

#### Applications:

- Numerical control

- Instrumentation

- Digital filtering

- Frequency synthesis

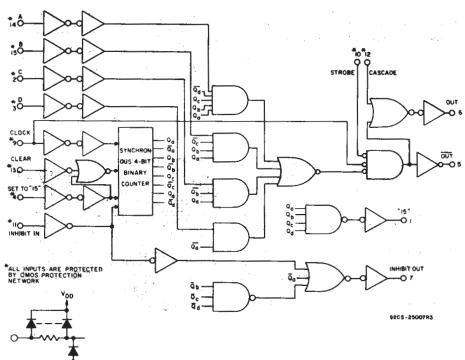

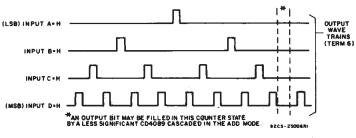

The CD4089B has an internal synchronous 4-bit counter which, together with one of the four binary input bits, produces pulse trains as shown in Fig. 2.

If more than one binary input bit is high, the resulting pulse train is a combination of the separate pulse trains as shown in Fig. 2.

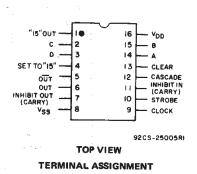

The CD4089B types are supplied in 16-lead ceramic dual-in-line packages (D and F suffixes), 16-lead dual-in-line plastic packages (E suffix), and in chip form (H suffix).

3

COMMERCIAL CMOS HIGH VOLTAGE ICs

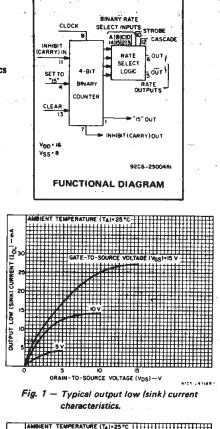

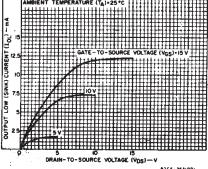

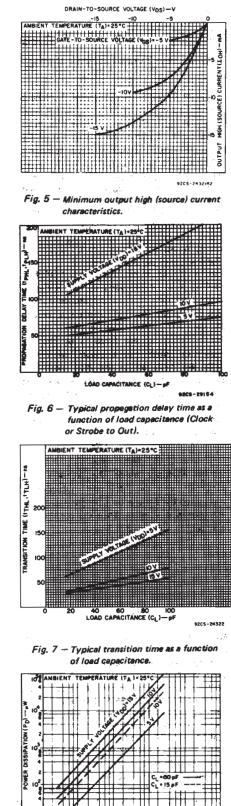

Fig. 2 - Minimum output low (sink) current

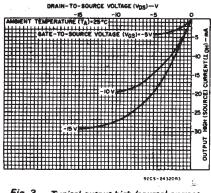

Fig. 3 — Typical output high (source) current characteristics.

| MAXIMUM RATINGS, Absolute-Maximum Values:                                  |                                       |

|----------------------------------------------------------------------------|---------------------------------------|

| DC SUPPLY-VOLTAGE RANGE, (VDD)                                             |                                       |

| Voltages referenced to VSS Terminal)                                       |                                       |

| INPUT VOLTAGE RANGE, ALL INPUTS                                            | -0.5V to V <sub>DD</sub> +0.5V        |

| DC INPUT CURRENT, ANY ONE INPUT                                            | ±10mA                                 |

| POWER DISSIPATION PER PACKAGE (PD):                                        | · · · · · · · · · · · · · · · · · · · |

| For $T_A = -55^{\circ}C$ to $+100^{\circ}C$                                |                                       |

| $For T_A = +100^{\circ}C$ to $+125^{\circ}C$                               |                                       |

| DEVICE DISSIPATION PER OUTPUT TRANSISTOR                                   |                                       |

| FOR TA = FULL PACKAGE-TEMPERATURE RANGE (All Package Ty                    | pes)                                  |

| OPERATING-TEMPERATURE RANGE (TA)                                           |                                       |

| STORAGE TEMPERATURE RANGE (Tstg)                                           |                                       |

| LEAD TEMPERATURE (DURING SOLDERING):                                       |                                       |

| At distance 1/16 $\pm$ 1/32 inch (1.59 $\pm$ 0.79mm) from case for 10s max | +265°C                                |

# CD4089B Types

**RECOMMENDED OPERATING CONDITIONS at**  $T_A = 25^{\circ}C$ , Except as Noted. For maximum reliability, nominal operating conditions should be selected so that operation is always within the following ranges:

| CHARACTERISTIC                                                 |                                      | V <sub>DD</sub> | LIŇ               | UNITS             |           |

|----------------------------------------------------------------|--------------------------------------|-----------------|-------------------|-------------------|-----------|

|                                                                |                                      | (V)             | Min.              | Max.              |           |

| Supply-Voltage Range (For T <sub>A</sub><br>Temperature Range) | ≠ Full Package-                      |                 | 3                 | 18                | V         |

| Set or Clear Pulse Width,                                      | tw                                   | 5<br>10<br>15   | 160<br>90<br>60   | 1 1 1             | ns        |

| Clock Pulse Width,                                             | tw                                   | 5<br>10<br>15   | 330<br>170<br>100 | 1,1               | ns        |

| Clock Frequency,                                               | <sup>f</sup> CL                      | 5<br>10<br>15   | dc                | 1.2<br>2.5<br>3.5 | MHz       |

| Clock Rise or Fall Time,                                       | <sup>t</sup> rCL <sup>or t</sup> fCL | 5,<br>10,15     | -                 | 15                | μs        |

| Inhibit In Setup Time,                                         | <sup>t</sup> SU                      | 5<br>10<br>15   | 100<br>40<br>20   | ·                 | ns<br>Ins |

| Inhibit In Removal Time,                                       | <sup>t</sup> REM                     | 5<br>10<br>15   | 240<br>130<br>110 | _ % *<br>_        | ns        |

| Set Removal Time,                                              | tREM                                 | 5<br>10<br>15   | 150<br>80<br>50   |                   | ris<br>I  |

| Clear Removal Time,                                            | <sup>t</sup> REM                     | 5<br>10<br>15   | 60<br>40<br>30    | _<br>1            | ns        |

Fig. 4 — Logic diagram.

Fig. 8 – Typical dynamic power dissipation as a function of input frequency.

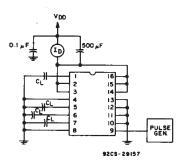

## DYNAMIC ELECTRICAL CHARACTERISTICS at T<sub>A</sub> = 25°C; Input t<sub>r</sub>, t<sub>f</sub> = 20 ns, C<sub>L</sub> = 50 pF, R<sub>1</sub> = 200 k $\Omega$

| CHARACTERISTIC                                               | TES<br>CONDIT |                      |                   | UNITS                 |                         |     |

|--------------------------------------------------------------|---------------|----------------------|-------------------|-----------------------|-------------------------|-----|

|                                                              |               | V <sub>DD</sub><br>V | Min.              | LIMITS<br>Typ.        | Max.                    |     |

| Propagation Delay Time, tPHL, tPLH<br>Clock to Out           |               | 5<br>10              |                   | 110<br>55             | 220<br>110              |     |

| Clock or Strobe to Out                                       |               | 15<br>5<br>10<br>15  |                   | 45<br>150<br>75<br>60 | 90<br>300<br>150<br>120 | ns  |

| Clock to Inhibit Out<br>High Level to Low Level              |               | 5<br>10<br>15        | _<br>_<br>_       | 360<br>160<br>110     | 720<br>320<br>220       | ns  |

| Low Level to High Level                                      |               | 5<br>10<br>15        |                   | 250<br>100<br>75      | 500<br>200<br>150       | ns  |

| Clear to Out                                                 |               | 5<br>10<br>15        |                   | 380<br>175<br>130     | 760<br>350<br>260       | ns  |

| Clock to "9" or "15" Out                                     |               | 5<br>10<br>15        | <br>              | 300<br>125<br>90      | 600<br>250<br>180       | ns  |

| Cascade to Out                                               |               | 5<br>10<br>15        |                   | 90<br>45<br>35        | 180<br>90<br>70         | ns  |

| Inhibit In to Inhibit Out                                    | :             | 5<br>10<br>15        | 1                 | 160<br>75<br>55       | 320<br>150<br>110       | ns  |

| Set to Out                                                   |               | 5<br>10<br>15        |                   | 330<br>150<br>110     | 660<br>300<br>220       |     |

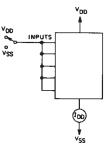

| Transition Time, <sup>t</sup> THL <sup>, t</sup> TLH         |               | 5<br>10<br>15        | _<br>_<br>_       | 100<br>50<br>40       | 200<br>100<br>80        | ns  |

| Maximum Clock Frequency, f <sub>CL</sub>                     |               | 5<br>10<br>15        | 1.2<br>2.5<br>3.5 | 2.4<br>5<br>7         |                         | MHz |

| Minimum Clock Pulse Width, t <sub>W</sub>                    |               | 5<br>10<br>15        | -                 | 165<br>85<br>50       | 330<br>170<br>100       | ns  |

| Clock Rise or Fall Time, t <sub>rCL</sub> , t <sub>fCL</sub> |               | 5<br>10<br>15        |                   |                       | 15<br>15<br>15          | μs  |

| Minimum Set or Clear Pulse Width, t <sub>W</sub>             |               | 5<br>10<br>15        | 1 1 1             | 80<br>45<br>30        | 160<br>90<br>60         | ns  |

| Minimum Inhibit-In Setup Time, t <sub>SU</sub>               |               | 5<br>10<br>15        | -                 | 50<br>20<br>10        | 100<br>40<br>20         | ns  |

| Minimum Inhibit In<br>Removal Time, <sup>t</sup> REM         | :             | 5<br>10<br>15        | -                 | 120<br>65<br>55       | 240<br>130<br>110       | ns  |

Fig. 9 - Dynamic power dissipation test circuit.

Fig. 10 - Quiescent device current test circuit.

92CS-27401R1

Fig. 11 — Input-current test circuit.

Fig. 12 - Input-voltage test circuit.

- \

. .-

| CHARACTERISTIC                               | TEST<br>CONDITIO |                      | UNITS     |                |                 |    |

|----------------------------------------------|------------------|----------------------|-----------|----------------|-----------------|----|

|                                              |                  | V <sub>DD</sub><br>V | Min.      | LIMITS         |                 |    |

| Minimum Set Removal Time, <sup>t</sup> REM   |                  | 5<br>10<br>15        |           | 75<br>40<br>25 | 150<br>80<br>50 | ns |

| Minimum Clear Removal Time, <sup>1</sup> REM |                  | 5<br>10<br>15        | `<br><br> | 30<br>20<br>15 | 60<br>40<br>30  | ns |

| Input Capacitance, C <sub>IN</sub>           | Any Input        | -                    | i - *     | 5              | 7.5             | pF |

## DYNAMIC ELECTRICAL CHARACTERISTICS at T<sub>A</sub> = 25°C (cont'd) Input t<sub>r</sub>, t<sub>f</sub> = 20 ns, C<sub>L</sub> = 50 pF, R<sub>L</sub> = 200 k $\Omega$

## STATIC ELECTRICAL CHARACTERISTICS

-2

| CHARAC-<br>TERISTIC             |                       | DITIO                  |                        | LIMITS AT INDICATED TEMPERATURES (°C) |       |       |       |       |             |      | NIT |

|---------------------------------|-----------------------|------------------------|------------------------|---------------------------------------|-------|-------|-------|-------|-------------|------|-----|

|                                 | V <sub>0</sub><br>(V) | V <sub>IN</sub><br>(V) | V <sub>DD</sub><br>(V) | 55                                    | 40    | +85   | +125  | Min.  | +25<br>Typ. | Max. | S   |

| •                               | _                     | 0,5                    | 5                      | 5                                     | 5     | 150   | 150   | -     | 0.04        | 5    |     |

| Quiescent<br>Device             | _                     | 0,10                   | 10                     | 10                                    | 10 .  | 300   | 300   | _     | 0.04        | 10   | μA  |

| Current,                        | -                     | 0,15                   | 15                     | 20                                    | 20    | 600   | 600   | -     | 0.04        | 20   | ~~~ |

| DD Max.                         | -                     | 0,20                   | 20                     | 100                                   | 100   | 3000  | 3000  | -     | 0.08        | 100  |     |

| Output Low                      | 0.4                   | 0,5                    | 5                      | 0.64                                  | 0.61  | 0.42  | 0.36  | 0.51  | 1           | -    |     |

| (Sink) Current                  | 0.5                   | 0,10                   | 10                     | 1.6                                   | 1.5   | 1.1   | 0.9   | 1.3   | 2.6         | -    |     |

| OL Min.                         | 1.5                   | 0,15                   | 15                     | 4.2                                   | 4     | 2.8   | 2.4   | 3.4   | 6.8         | -    | 1   |

| Output High                     | 4.6                   | 0,5                    | 5                      | -0.64                                 | -0.61 | -0.42 | -0.36 | -0.51 | -1          | _    | mA  |

| (Source)                        | 2.5                   | 0,5                    | 5                      | 2                                     | -1.8  | -1.3  | -1.15 | -1.6  | -3.2        | -    |     |

| Current,                        | 9.5                   | 0,10                   | 10                     | - 1.6                                 | -1.5  | -1.1  | -0.9  | -1.3  | -2.6        | -    | 1   |

| <sup>1</sup> OH <sup>Min.</sup> | 13.5                  | 0,15                   | 15                     | -4.2                                  | -4    | -2.8  | - 2.4 | -3.4  | -6.8        | -    |     |

| Output Voltage:                 | -                     | 0,5                    | 5                      | 0.05                                  |       |       |       |       | 0           | 0.05 |     |

| Low Level,                      | -                     | 0,10                   | 10                     |                                       | 0.05  |       |       |       | 0           | 0.05 | v   |

| VOL Max.                        | _                     | 0,15                   | 15                     | 0.05                                  |       |       |       | -     | 0           | 0.05 |     |

| Output                          | -                     | 0,5                    | 5                      |                                       | 4     | 95    |       | 4.95  | 5           | _    |     |

| Voltage:<br>High-Level,         | -                     | 0,10                   | 10                     | -                                     | 9     | 95    |       | 9.95  | 10          | -    |     |

| VOH Min.                        | -                     | 0,15                   | 15                     |                                       | 14    | .95   |       | 14.95 | 15          | -    |     |

| Input Low                       | 0.5,4.5               | -                      | 5                      |                                       |       | 1.5   |       | -     | -           | 1.5  |     |

| Voltage                         | 1,9                   | _                      | 10                     | •                                     |       | 3     |       |       |             | 3    | ]   |

| VIL Max.                        | 1.5,13.5              | -                      | 15                     |                                       |       | 4     |       | -     |             | 4    | ] v |

| Input High                      | 0.5,4.5               | ·                      | 5                      |                                       |       | 3.5   |       | 3.5   | . –         | -    |     |

| Voltage,                        | 1,9                   | ·                      | 10                     |                                       |       | 7     |       | 7     | -           | -    |     |

| V <sub>IH</sub> Min.            | 1.5,13.5              | _                      | 15                     |                                       |       | 11    |       | 11    | -           | -    |     |

| Input Current                   | -                     | 0,18                   | 18                     | ±0.1                                  | ±0.1  | ±1    | ±1    | -     | ±10-5       | ±0.1 | μA  |

|   |                                                                                 |   |   |     |           |     | TRU | JTH TA | BLE   |                                   |          |            |             |

|---|---------------------------------------------------------------------------------|---|---|-----|-----------|-----|-----|--------|-------|-----------------------------------|----------|------------|-------------|

|   | INPUTS                                                                          |   |   |     |           |     |     |        | OUTPL | JTS                               |          |            |             |

|   | Number of Pulses or<br>Input Logic Level<br>{0 = Low; 1 = High; X = Don't Care} |   |   |     |           |     |     |        | 0     | umber of<br>utput Log<br>= Low; F | ic Level | 1          |             |

| D | С                                                                               | В | Α | CLK | INH<br>IN | STR | CAS | CLR    | SET   | OUT                               | OUT      | INH<br>OUT | "15"<br>OUT |

| 0 | 0                                                                               | 0 | 0 | 16  | 0         | 0   | 0   | 0      | 0     | L                                 | н        | 1          | 1           |

| 0 | 0                                                                               | 0 | 1 | 16  | 0         | 0   | 0   | 0      | 0     | 1                                 | 1        | 1          | 1           |

| 0 | 0                                                                               | 1 | 0 | 16  | 0         | 0   | 0   | [ 0    | 0     | 2                                 | 2        | 1          | 1.          |

| 0 | 0                                                                               | 1 | 1 | 16  | 0         | 0   | 0   | 0      | 0     | - 3                               | . 3      | 1.         | 1           |

| 0 | 1                                                                               | 0 | 0 | 16  | 0         | 0   | 0   | 0      | 0     | 4                                 | 4        | 1          | 1           |

| 0 | 1                                                                               | 0 | 1 | 16  | 0         | 0   | 0   | 0      | 0     | 5                                 | 5        | 1          | 1           |

| 0 | 1                                                                               | 1 | 0 | 16  | 0         | 0   | 0   | 0      | 0     | 6                                 | 6        | 1          | 1           |

| 0 | 1                                                                               | 1 | 1 | 16  | 0         | 0   | 0   | 0      | 0     | 7                                 | 7        | 1          | 1           |

| 1 | 0                                                                               | 0 | 0 | 16  | 0         | 0   | 0   | 0      | 0     | 8                                 | 8        | 1          | 1           |

| 1 | 0                                                                               | 0 | 1 | 16  | 0         | 0   | 0   | 0      | 0     | 9                                 | 9        | 1          | 1           |

| 1 | 0                                                                               | 1 | 0 | 16  | 0         | . 0 | 0   | 0      | 0     | 10                                | 10       | 1          | 1           |

| 1 | 0                                                                               | 1 | 1 | 16  | 0         | 0   | 0   | 0      | 0     | 11                                | 11       | . 1        | 1           |

| 1 | 1                                                                               | 0 | 0 | 16  | 0         | 0   | 0   | 0      | 0     | 12                                | 12       | 1          | 1           |

| 1 | 1                                                                               | 0 | 1 | 16  | 0         | 0   | 0   | 0      | 0     | 13                                | 13       | 1          | 1           |

| 1 | 1                                                                               | 1 | 0 | 16  | 0         | 0   | 0   | 0      | 0     | 14                                | 14       | 1          | 1           |

| 1 | 1                                                                               | 1 | 1 | 16  | 0         | 0   | 0   | 0      | 0     | 15                                | 15       | 1          | 1           |

| x | x                                                                               | x | x | 16  | 1         | 0   | ~ 0 | 0      | 0     | t                                 | †        | н          | +           |

| X | x                                                                               | х | x | 16  | 0         | 1   | 0   | 0      | 0     | L                                 | н        | 1          | 1           |

| X | х                                                                               | х | х | 16  | 0         | 0   | 1   | 0      | 0     | н                                 | *        | 1          | 1           |

| 1 | х                                                                               | х | х | 16  | 0         | 0   | 0   | 1      | 0     | 16                                | 16       | н          | L           |

| 0 | х                                                                               | х | X | 16  | 0         | 0   | 0   | 1      | 0     | L                                 | н        | н          | L           |

| X | х                                                                               | Х | X | 16  | 0 ·       | 0   | 0   | x      | 1     | L                                 | н        | L          | н           |

TOUTH TADLE

COMMERCIAL CMOS HIGH VOLTAGE ICs

3

\* Output same as the first 16 lines of this truth table (depending on values of A, B, C, D).

<sup>†</sup> Depends on internal state of counter.

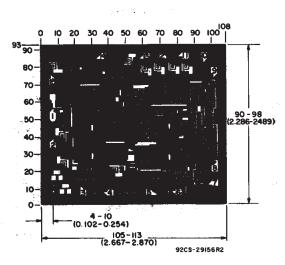

Dimensions and Pad Layout for CD4089BH

Fig. 15 - Timing diagram.

Dimensions in parentheses are in millimeters and are derived from the basic inch dimensions as indicated. Grid graduations are in mils  $(10^{-3} \text{ inch})$ .

### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1998, Texas Instruments Incorporated