# ST52T420/E420

# 8-BIT $DuaLogic\hat{O}$ MCU WITH 4K BYTES OTP/EPROM, 128 BYTES RAM, WDG, ADC, 3 TIMER/PWM DRIVERS

#### **PRELIMINARY DATA**

- Digital Microcontroller with Fuzzy capabilities,

4 kbytes internal EPROM, 128 bytes of Data

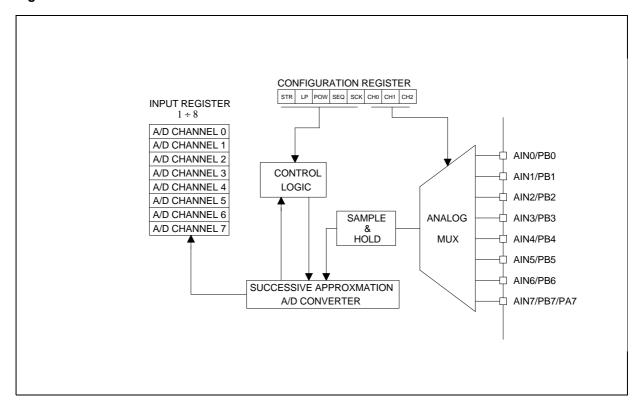

- On-chip 8 bit A/D Converter with an 8-channel multiplexer.

- 19 Configurable I/O PINs.

- Hardware multiplication and division.

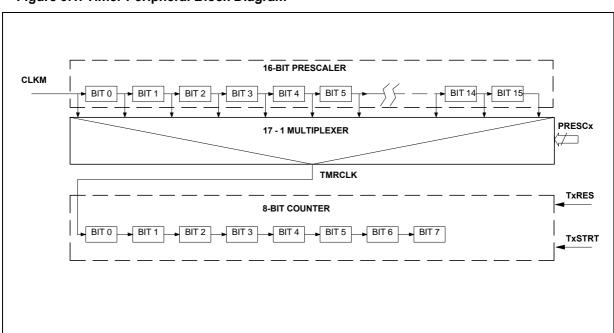

- Two Programmable Timer/PWM with internal 16-bit Prescaler, featuring:

- PWM output and Pulse generator mode

- Complementary Outputs

- One Programmable Timer/PWM with internal 16-bit Prescaler, featuring:

- 1 Input capture

- 1 Output compare

- External / Internal Clock

- PWM output and Pulse generator mode

- Complementary Outputs

- Watchdog timer.

- Capability to perform boolean, arithmetic operations and fuzzy algorithms.

- 46 basic instructions.

- Power Saving Features.

- Software tools and Emulators availability

- EPROM readout protection

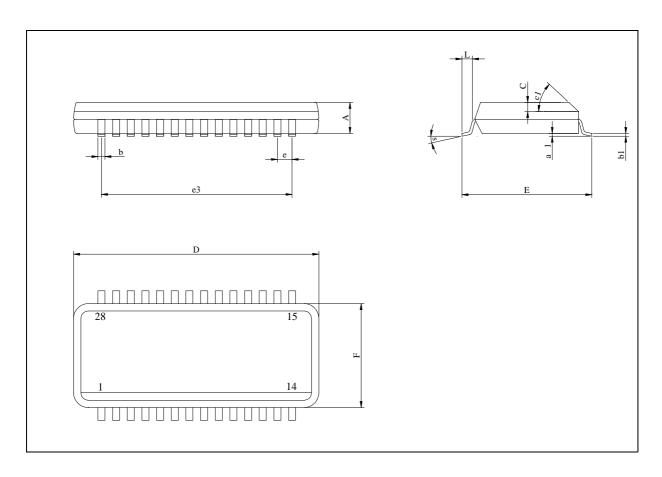

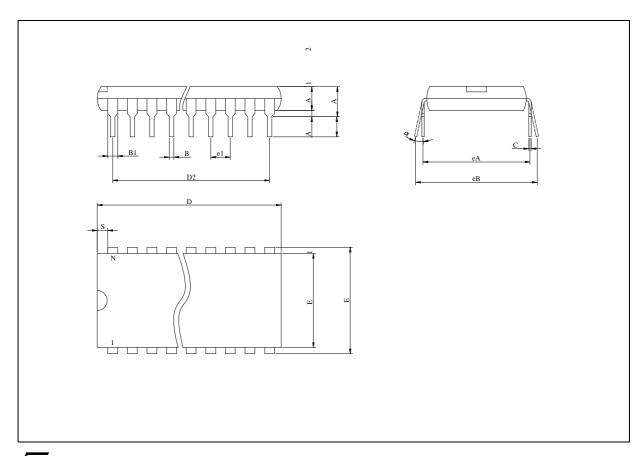

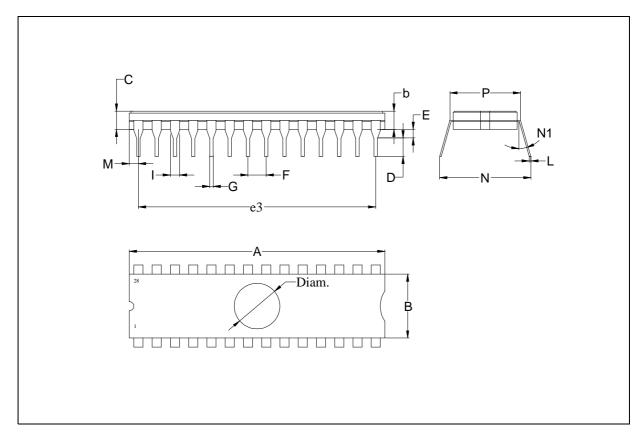

- 28 pin Plastic Package

| Features               | ST52x420G0         | ST52x420G1          | ST52x420G2 |  |  |

|------------------------|--------------------|---------------------|------------|--|--|

| Program Memory - bytes | 1k                 | 2k                  | 4k         |  |  |

| RAM - bytes            |                    | 128                 |            |  |  |

| PWM / TIMER            |                    | 3                   |            |  |  |

| ADC                    | 8 channels / 8 bit |                     |            |  |  |

| Other Peripherals      |                    | Watchdog            |            |  |  |

| Operating Supply       |                    | 3 to 5.5 V          |            |  |  |

| CPU frequency          |                    | up to 20 Mhz        |            |  |  |

| Temperature reange     |                    | -45 to +85 °C       |            |  |  |

| Packages               | PDI                | P28 - PSO28 - CDIP2 | 28W        |  |  |

January 2001 1/120

#### **GENERAL DESCRIPTION**

ST52x420 is a member of the ST52xxx family of 8-bit  $DuaLogic \hat{O}$  microcontrollers.

It is available in different versions, depending on memory size and peripheral.

ST52x420 is able to perform, in an efficient way, both boolean and fuzzy algorithms, in order to reach the best performances that the two methodologies allow. It is produced by STMicroelectronics using the reliable high performance CMOSM6XE ( $0.5\mu m$ ) process.

Thanks to Fuzzy Logic, ST52x420 allows to describe a problem using a linguistic model instead of a mathematical model. In this way it is very useful and easy to modelize complex systems with very high accuracy.

The linguistic approach is based on a set of IF-THEN rules, describing the control behaviour, and on Membership Functions associated to input and output variables.

Fuzzy Inference is a set of operations which computes the output values according with the truth values of the involved rules.

The flexible I/O configuration of ST52x420 allows to interface with a wide range of external devices, like D/A converters or power control devices.

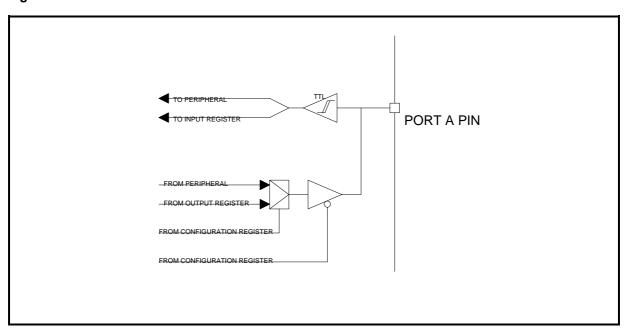

ST52x420 pins are configurable, allowing to set the input, or output, signals on each single pin, as shown in figures 1.3 and 1.4.

The OTP (One Time Programmable) device is fully compatible with the EPROM windowed version, which may be used for the prototyping and pre-production phases of development.

The EPROM memory can be locked by user to avoid external operations.

It is possible to perform operations on data stored in the RAM (128 bytes), allowing to directly combine new inputs and feedback signals.

It is possible to store up to 341 Membership Functions, with triangular and trapezoidal shapes, or singleton values.

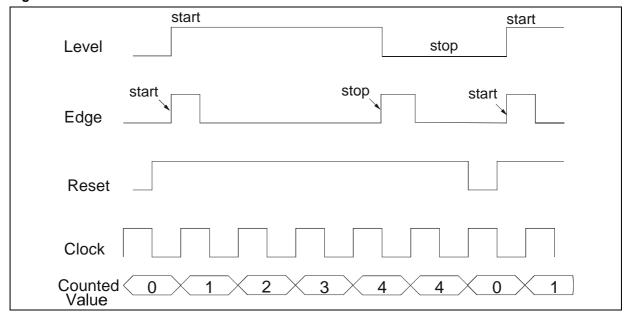

Three TIMER/PWM drivers allow to manage power devices and timing signals, implementing different operating modes and high frequency PWM (Pulse Width Modulation) controls.

One of these programmable timers, with Internal Prescaler, can use internal or external START/STOP signals and clock.

An internal programmable watchdog is available to avoid loop errors and reset the microcontroller.

In order to reduce the energy consumption, ST52x420 is able to perform two different power saving features: Wait mode and Halt mode.

The EPROM contains the microcontroller configuration, in terms of I/O number, microcode, Fuzzy Rules and Membership Functions (MFs).

ST52x420 processes inputs and produces the related outputs according to the configuration loaded during the programming phase (stored into the EPROM).

ST52x420 includes an 8-bit Analog to Digital Converter with an 8-analog channel Multiplexer.

A powerful development environment consisting of board and software allows an easy configuration and use of ST52x420.

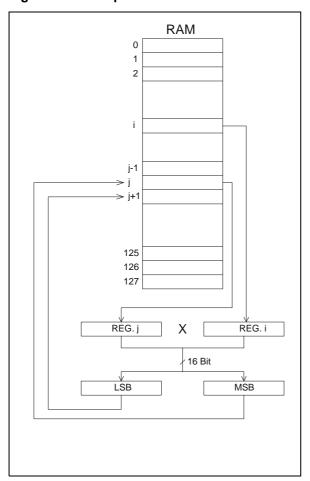

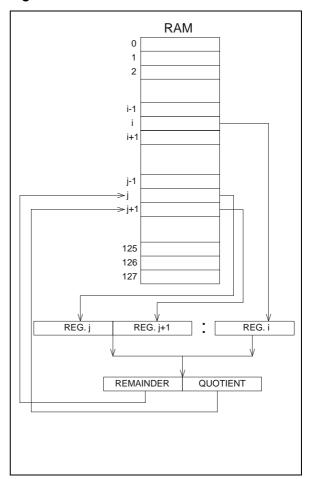

It is possible to perform 16 bit over 8 bit arithmetical divisions, with 8 bit result and 8 bit remainder, and 8 bit by 8 bit arithmetical multiplications, with 16 bit result.

ST52x420 is fully supported by FUZZYSTUDIO<sup>TM</sup>4 allowing to graphically design a project and obtain an optimized microcode.

ST52x420 exploits a STMicroelectronics patented strategy to store the MFs in its internal memory.

# **FUNCTIONAL DESCRIPTION**

ST52x420 works in two modes according to the control signal level.

ST52x420 is a programmable product and its functionment phases are:

- Memory Programming Phase

- Working Phase

These phases are selected by using the following signals (see pins description):

- RESET

- TEST

- Vpp

#### **Memory Programming Phase**

ST52x420 memory is loaded in Memory Programming Phase. All fuzzy and standard instructions are written inside the memory.

This phase starts with the setting of the control signals as follows:

RESET=Vss

TEST=Vss

V<sub>PP</sub>=12 V

When this phase starts, ST52x420 core is set to the RESET status. This allows to program and/or to test the internal Eprom. The signal INC\_ADD is used to increment the address of the memory (see Eprom programming).

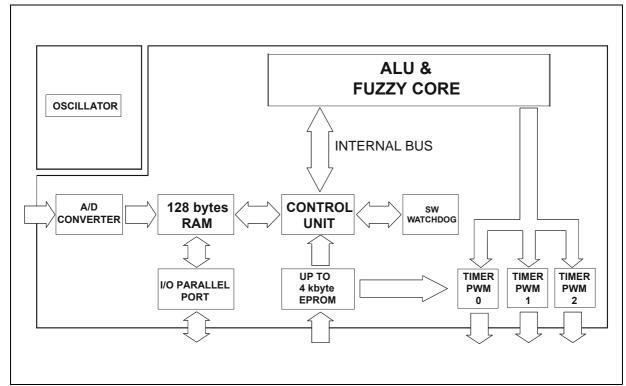

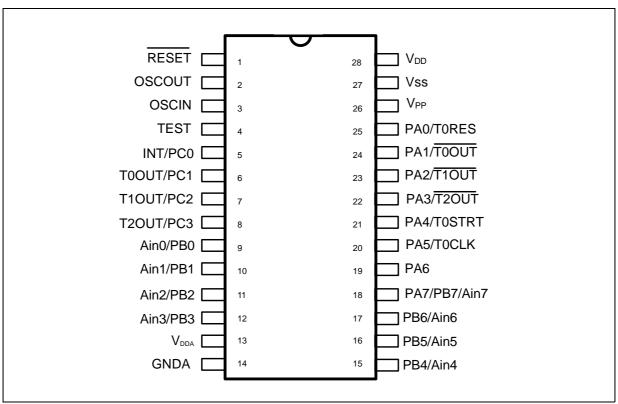

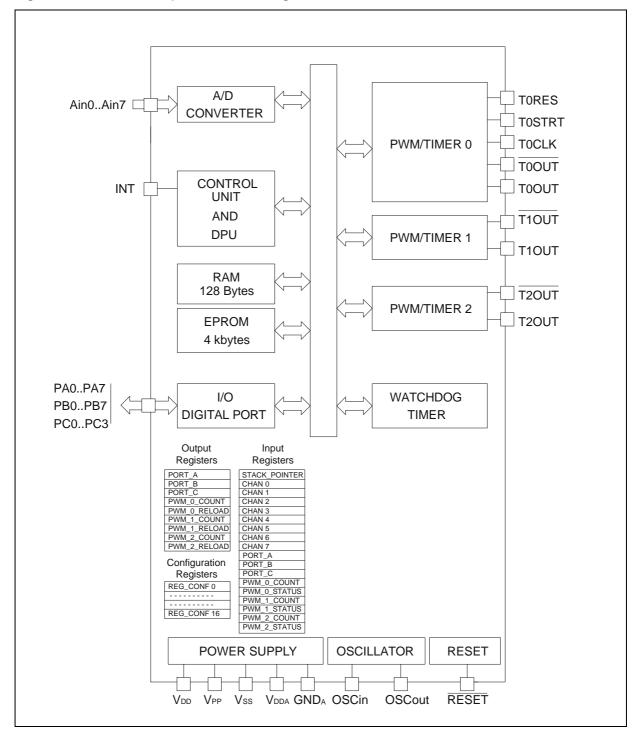

Figure 1.1 ST52x420 Architectural Block Diagram

# **Working Mode**

In this mode the control signals are the following :

RESET=V<sub>DD</sub>

TEST=Vss

V<sub>PP</sub>=Vss

The processor starts the working phase following the instructions which have been previously loaded in the memory.

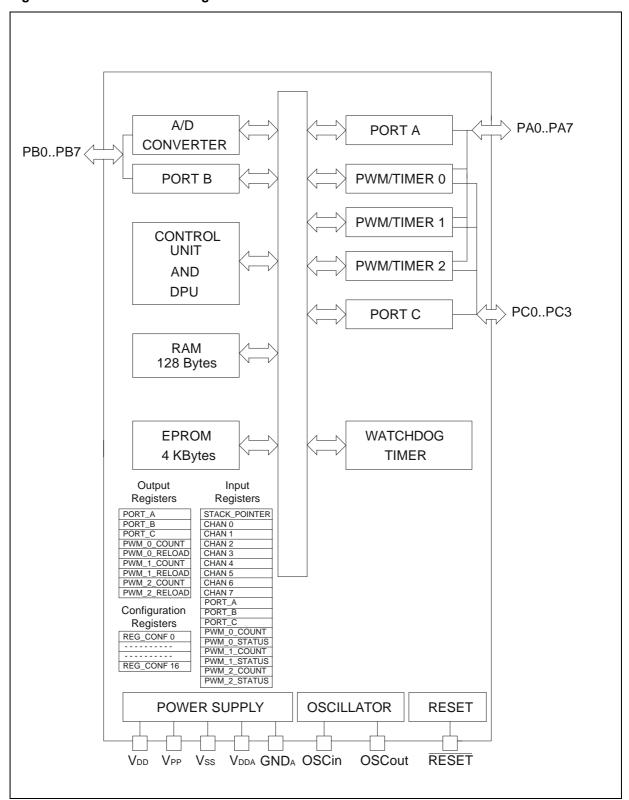

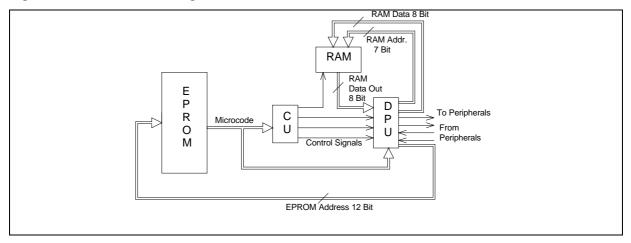

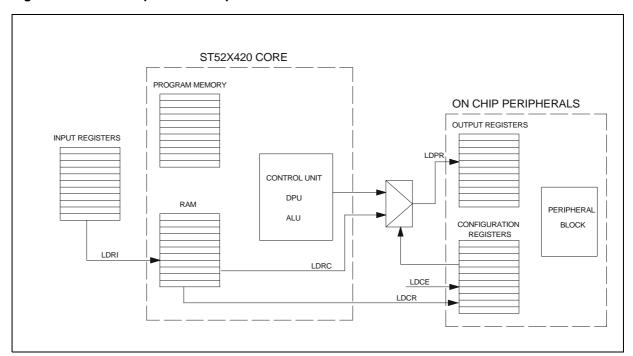

Figure 1.2 shows the internal structure of ST52x420. It is composed by one computational block: the CONTROL UNIT (CU) / DPU block, which allows the implementation of the fuzzy calculus and the performing of boolean functions.

The CU/DPU is able to manage up to 341 different Membership Functions for the fuzzy rules antecedent part. The rules consequents are "crisp" values (real numbers). The number of possible rules is related with the dimensions of the implemented standard algorithm. Smaller standard algorithms allow to define bigger fuzzy algorithms with more rules and viceversa. The 4 kbytes of the Eprom are then shared between fuzzy and standard algorithms.

The Control Unit (CU) reads the information and the status incoming from the peripherals.

The arithmetic calculus can be performed on these values by using the internal CU and the 128 bytes RAM, which supports all computations.

The inputs of the peripherals can be the fuzzy and/or arithmetic outputs, or the values contained in Data RAM and EPROM locations.

**AY/**

Figure 1.2 ST52x420 Block Diagram

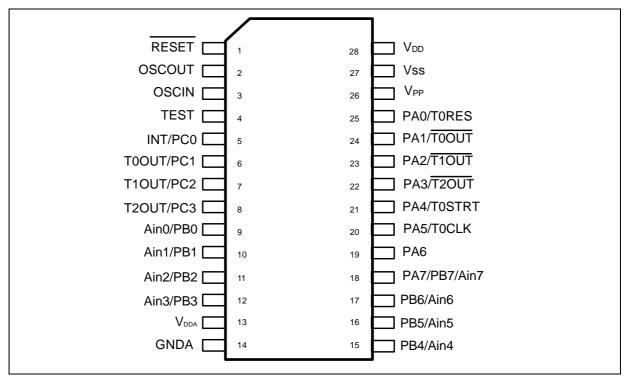

Figure 1.3a. ST52X420 SO28 Pin Configuration

Figure 1.4a. ST52X420 DIP28 Pin Configuration

Table 1.1 ST52x420 SO-28 and DIP-28 Pin Configuration

| PIN | NAME            | TYPE | Programming Phase                           | Working Phase                                |

|-----|-----------------|------|---------------------------------------------|----------------------------------------------|

| 1   | RESET           | 1    | General Reset                               | General Reset                                |

| 2   | OSCOUT          |      | Oscillator Output                           | Oscillator Output                            |

| 3   | OSCIN           |      | Oscillator Input                            | Oscillator Input                             |

| 4   | TEST            |      | Test Mode Selector                          | Test Mode Selector                           |

| 5   | INT / PC0       | I/O  | PHASE signal                                | External interrupt / Digital I/O             |

| 6   | T0OUT / PC1     | I/O  |                                             | Timer/PWM 0 output / Digital I/O             |

| 7   | T1OUT / PC2     | I/O  |                                             | Timer/PWM 1 output / Digital I/O             |

| 8   | T2OUT / PC3     | I/O  |                                             | Timer/PWM 2 output / Digital I/O             |

| 9   | Ain0 / PB0      | I/O  | Address RESET                               | Analog Input / Digital I/O                   |

| 10  | Ain1 / PB1      | I/O  | Address INCREMENT                           | Analog Input / Digital I/O                   |

| 11  | Ain2 / PB2      | I/O  | Configuration RESET                         | Analog Input / Digital I/O                   |

| 12  | Ain3 / PB3      | I/O  | Configuration INCREMENT                     | Analog Input / Digital I/O                   |

| 13  | $V_{DDA}$       |      | Analog Power Supply                         | Analog Power Supply                          |

| 14  | GNDA            |      | Analog Ground                               | Analog Ground                                |

| 15  | Ain4 / PB4      | I/O  |                                             | Analog Input / Digital I/O                   |

| 16  | Ain5 / PB5      | I/O  |                                             | Analog Input / Digital I/O                   |

| 17  | Ain6 / PB6      | I/O  |                                             | Analog Input / Digital I/O                   |

| 18  | Ain7 / PB7/ PA7 | I/O  | I/O EPROM Data                              | Analog Input / Digital I/O                   |

| 19  | PA6             | I/O  | I/O EPROM Data                              | Digital I/O                                  |

| 20  | T0CLK / PA5     | I/O  | I/O EPROM Data                              | Timer/PWM 0 clock / Digital I/O              |

| 21  | T0STRT / PA4    | I/O  | I/O EPROM Data                              | Timer/PWM 0 start/stop / Digital I/O         |

| 22  | T2OUT / PA3     | I/O  | I/O EPROM Data                              | Timer/PWM 2 inverted output /<br>Digital I/O |

| 23  | T10UT / PA2     | I/O  | I/O EPROM Data                              | Timer/PWM 1 inverted output /<br>Digital I/O |

| 24  | TOOUT / PA1     | I/O  | I/O EPROM Data                              | Timer/PWM 0 inverted output /<br>Digital I/O |

| 25  | TORES / PAO     | I/O  | I/O EPROM Data                              | Timer/PWM 0 Reset / Digital I/O              |

| 26  | $V_{PP}$        |      | EPROM Programming<br>Power supply (12V ±5%) | EPROM V <sub>DD</sub> or Vss                 |

| 27  | V <sub>SS</sub> |      | Digital Ground                              | Digital Ground                               |

| 28  | $V_{DD}$        |      | Digital Power Supply                        | Digital Power Supply                         |

#### 1.2 PIN DESCRIPTION

ST52x420 pins are configurable by means of configuration registers.

**V**DD, **V**SS, **V**DDA, **GNDA**, **V**PP. In order to avoid noise disturbances, the power supply of the digital part is kept separated from the power supply of the analog part.

V<sub>DD</sub>. Main Power Supply Voltage.

In the ST52x410 version the two  $V_{DD}$  pins must be connected togheter .

Vss. Digital Circuit Ground.

In the ST52x410 version the two  $V_{SS}$  pins must be connected togheter

**V**DDA. Analog VDD of the Analog to Digital Converter.

**GNDA**. Analog Vssa of the Analog to Digital Converter. *Must be tied to Vss.*

**VPP.** Main Power Supply for the internal EPROM. (12 V  $\pm$  5% in programming phase) and Operating Modes selector. During the Programming phase (programming) VPP must be set at 12V. In the Working phase VPP must be equal to VSS.

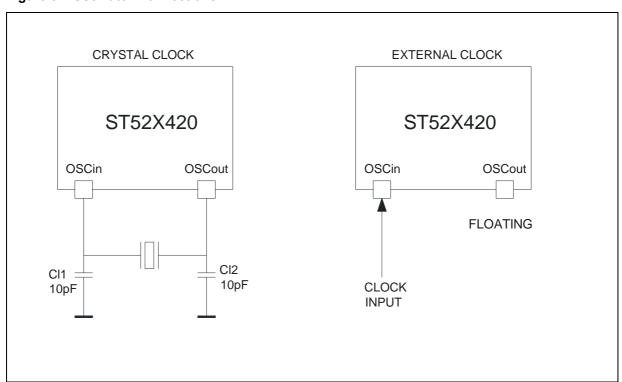

**OSCin** and **OSCout.** These pins are internally connected with the on-chip oscillator circuit. A quartz crystal or a ceramic resonator can be connected between these two pins in order to allow the correct operations of ST52x420 with various stability/cost trade-offs. An external clock signal can be applied to OSCin, in this case OSCout must be kept floating.

**RESET**. This signal is used to restart ST52x420 at the beginning of its program. It also allows to select the program mode for the EPROM.

**Ain0-Ain7.** These 8 lines are connected to the inputs of the analog multiplexer. They allow to acquire 8 analog inputs. During the Programming phase, Ain0, Ain1, Ain2 and Ain3 are used to manage EPROM operation.

**PA0-PA7**, **PB0-PB7**, **PC0-PC3**. These lines are organized as I/O port. Each pin can be configured as input or output. During the Programming phase PA port is used for the EPROM data read/write.

**TORES**, **TOCLK**, **TOSTRT**. These pins are related with the internal Programmable Timer/PWM 0. This Timer can be reset externally by using TORES. In Working Mode, TORES resets the address counter of the Timer. TORES is active at low level.

The Timer 0 Clock can be the internal clock or can be supplied externally by using the pin T0CLK.

An external Start/Stop signal can be used to control the Timer through the pin T0STRT.

**T00UT, T10UT, T20UT.** The TIMER/PWM outputs are available on these pins.

**TOOUT**, **T1OUT**, **T2OUT**. The TIMER/PWM inverted outputs are available on these pins.

**TEST**. It enables the testing functionalities; during the Programming and Working phase it must be set to Vss

**INT**. This pin is used to start the External Interrupt routine.

#### **2 INTERNAL ARCHITECTURE**

ST52x420 is made up by the following blocks and peripherals:

- Control Unit (CU) and Data Processing Unit (DPU)

- ALU / Fuzzy Core

- EPROM

- 128 Byte RAM

- Clock Oscillator

- Analog Multiplexer and A/D Converter

- 3 PWM / Timers

- Digital I/O ports

### ST52x420 Operating Modes

ST52x420 works in two modes, Programming and Working Modes, depending on the control signals level RESET, TEST and  $V_{PP}$ .

The Operating modes are selected by setting the control signal level as specified in the Control Signals Setting table.

**Table 2.1. Control Signals setting**

| Control<br>Signal | Programming | Reset | Working  |

|-------------------|-------------|-------|----------|

| RESET             | Vss         | Vss   | $V_{DD}$ |

| TEST              | Vss         | Vss   | Vss      |

| Vpp               | 12 V        | Vss   | Vss      |

# 2.1 CONTROL UNIT and DATA PROCESSING UNIT

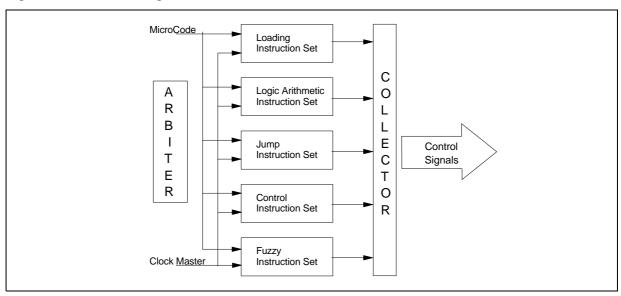

The Control Unit (CU) formally includes five main blocks. Each block decodes a set of instructions then generating the appropriate control signals.

The main parts of the CU are shown in the figures 2.1 and 2.2.

The five different parts of the CU manage the Loading, Logic/Arithmetic, Jump, Control and Fuzzy instructions set.

The block called "Collector" manages the signals coming from the different parts of the CU then defines the signals for the Data Processing Unit (DPU) and for the different peripherals of the microcontroller.

The block called "Arbiter" manages the different parts of the CU in order to have only one part of the system activated during the working mode.

The CU structure is very flexible. It was designed with the aim to easily adapt the core of the microcontroller to the market needs. New instructions set or new peripherals can be easily included without changing the structure of the microcontroller then mantaining the code compatibility.

The CU reads the stored instructions on the EPROM (Fetch) and decodifies them. The Arbiter according to the instructions type, activates one of the main blocks of the CU. Then all the control signals for the DPU are generated.

A set of 46 different arithmetic, fuzzy and logic instructions is available. Each instruction requires from 6 (fuzzy instructions) up to 26 (DIVISION) clock pulses to be performed.

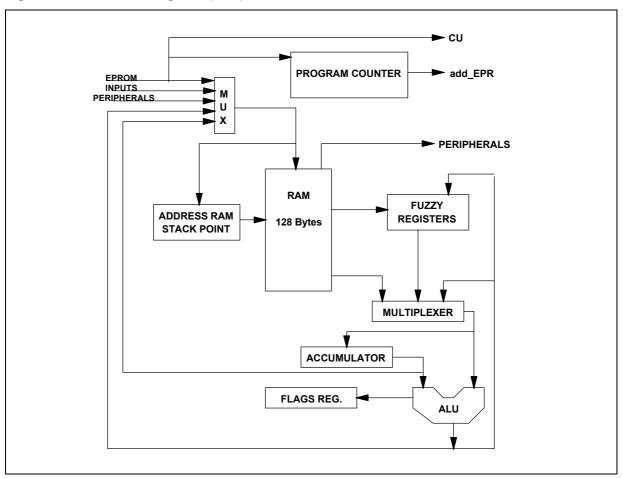

The DPU receives, stores and sends the instructions coming from the EPROM, the RAM or from the peripherals in order to execute them.

Figure 2.1 CU/DPU Block diagram

Figure 2.2 CU Block Diagram

Figure 2.3 Data Processing Unit (DPU)

Figure 2.4 ST52x420 Peripherals Block Diagram

Note: ST52x410 version does not have the A/D Converter.

# 2.1.1 Program Counter

The Program Counter (PC) is a 12-bit register that contains the address of the next memory location to be processed by the core. This memory location may be an opcode, an operand or an address of an operand.

The 12-bit length allows the direct addressing mode of 4096 bytes in the program space.

After having read the current instruction address, the PC value is incremented. The result of this operation is shifted back into the PC.

The PC can be changed in the following ways:

■ JP (Jump) instruction PC = Jump Address

■ Interrupt PC = Interrupt Vector

■ RETI instruction PC = Pop (stack)

■ Reset PC = Reset Vector

■ Normal Instruction PC = PC + 1

# 2.1.2 Flags

The ST52x420 core includes different sets of flags. Each set of flags consist of a CARRY flag (C), a ZERO flag (Z) and SIGN flag (S).

Each interrupt level and the main level have their own set of flags, that are saved in the STACK together with the Program Counter.

If an interrupt occurs, the ST52x420 core uses the associated set of flags, and stores, in the STACK, the actual set in use .

These flags are restored from the STACK automatically, when a RETI instruction is executed.

The flags are not cleared during the context switching and remain in the state they were at the exit of the last interrupt routine switching.

**Note:** A CALL subroutine does not store in the STACK the current set of flags. For this reason a RET instruction, consequent to a CALL instruction, does not affect, the set of flags in use.

Carry flag is set when an overflow occurs during arithmetic operations, otherwise it is cleared.

Sign flag is set when an underflow occurs during arithmetic operations, otherwise it is cleared.

Zero flag is set when a result equal to 0 occurs during arithmetic operations, otherwise it is cleared.

Figure 2.5 Address Spaces Description

#### 2.2 ADDRESS SPACES

ST52x420 has five separate address spaces:

■ RAM: 128 Bytes

Input Registers: 18 8-bit registersOutput Registers 9 8-bit registers

■ Configuration Registers: 17 8-bit registers

■ Program memory up to 4K Bytes

The Program memory will be described in further details in the MEMORY section

# 2.2.1 RAM and STACK

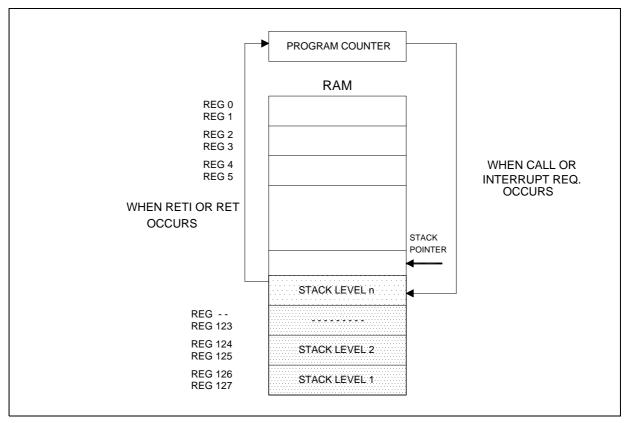

The RAM memory consists of 128 general purpose 8-bit RAM registers.

All the registers in the RAM can be specified by using a decimal address, e.g. 0 identifies the first register of the RAM.

A RAM register is read in 2 cycles and is written in 3 cycles. To read or write the RAM registers the LOAD instructions must be used. See table 2.6

Each interrupt level has its own set of flags, that is saved in the STACK together with the Program

Counter. These flags are restored from the STACK automatically, when a RETI instruction is executed.

When the instructions like Interrupt request or CALL are executed, a STACK level is used to push the PC and flags.

The STACK is located in the RAM. For each level of stack 2 bytes of the RAM are used. The values of this stack are stored from the last RAM register (address 127). The maximum level of stack must be less than 64.

The STACK POINTER indicates the first level available to store data. When a subroutine call or interrupt request occurs, the content of the PC and the current set of flag are stored into the level located by the STACK POINTER. When a subroutine or interrupt return occurs (RET or RETI instructions), the data stored in the highest stack level are restored back into the PC and current flags. These operating modes are described in the Figure 2.6.

**Note:** User must take care to avoid the overwriting of the RAM locations, where the STACK could be stored.

# 2.2.2 Input Registers Bench

The Input Registers (IR) bench consists of 18 8-bit registers containing data or status of the peripherals.

All the registers can be specified by using a decimal address, e.g. 0 identifies the first register of the IR. The assembler instruction:

LDRI RAM\_Reg. IR\_i

loads the value of the i-th IR in the RAM location identified by the address RAM\_Reg.

The first input register, STACK\_POINTER, is dedicated to store the value of the stack pointer. The next 8 registers (ADC\_OUT\_0:7) of the IR are dedicated to the 8 converted values coming from the ADC. The last 9 registers contain data from the I/O ports and PWM/Timers. The following table summarises the IR address and the relative peripheral.

For simplicity reasons a mnemonic name is assigned to the registers. The same name is used in FUZZYSTUDIO<sup>TM</sup>4.0 development tools.

**Table 2.2 Input Registers**

| IR MNEMONIC NAME | PERIPH                         | IERALS |

|------------------|--------------------------------|--------|

| STACK_POINTER    | STACK POINTER                  | 0      |

| CHAN 0           | A/D CHANNEL 0                  | 1      |

| CHAN 1           | A/D CHANNEL 1                  | 2      |

| CHAN 2           | A/D CHANNEL 2                  | 3      |

| CHAN 3           | A/D CHANNEL 3                  | 4      |

| CHAN 4           | A/D CHANNEL 4                  | 5      |

| CHAN 5           | A/D CHANNEL 5                  | 6      |

| CHAN 6           | A/D CHANNEL 6                  | 7      |

| CHAN 7           | A/D CHANNEL 7                  | 8      |

| PORT_A           | PORT A INPUT REGISTER          | 9      |

| PORT_B           | PORT B INPUT REGISTER          | 10     |

| PORT_C           | PORT C INPUT REGISTER          | 11     |

| PWM_0_COUNT      | PWM/TIMER 0 COUNTER            | 12     |

| PWM_0_STATUS     | PWM/TIMER 0 STATUS<br>REGISTER | 13     |

| PWM_1_COUNT      | PWM/TIMER 1 COUNTER            | 14     |

| PWM_1_STATUS     | PWM/TIMER 1 STATUS<br>REGISTER | 15     |

| PWM_2_COUNT      | PWM/TIMER 2 COUNTER            | 16     |

| PWM_2_STATUS     | PWM/TIMER 2 STATUS<br>REGISTER | 17     |

The input register PORT\_C contains 4 bits.

# 2.2.3 Configuration Registers

The ST52x420 Configuration Registers allow to configure all the blocks of the fuzzy microcontroller. Table 2.3 describes the functions and the related peripherals of each Configuration Registers. By using the load instructions it is possible to set the Configuration Registers by using

values stored in the Program Memory (EPROM) or in the RAM.

**Table 2.3. Configuration Registers description**

| CONFIGURATION REGISTER | PERIPHERAL         | DESCRIPTION                                                           |

|------------------------|--------------------|-----------------------------------------------------------------------|

| REG_CONF 0             | INTERRUPT MASK     | Interrupts mask setting                                               |

| REG_CONF 1             | INTERRUPT PRIORITY | Interrupts priority setting                                           |

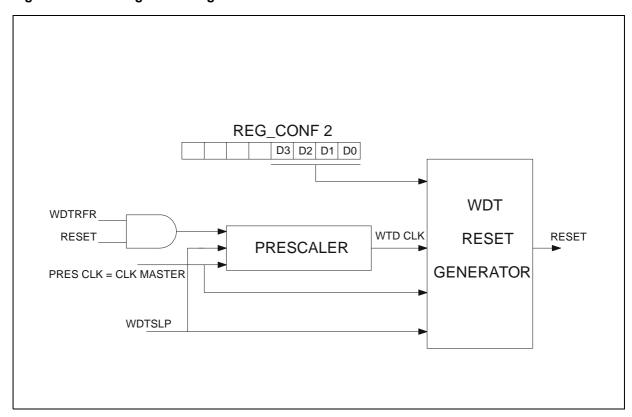

| REG_CONF 2             | WATCHDOG TIMER     | Watchdog Timer configuration                                          |

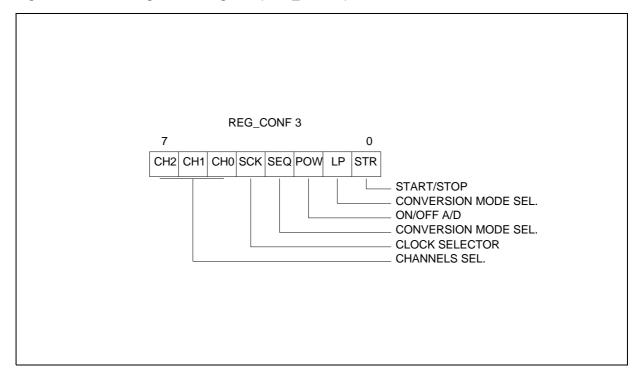

| REG_CONF 3             | A/D CONVERTER      | A/D configuration                                                     |

| REG_CONF 4             | PORT A             | Set the relative bit like digital input or digital output             |

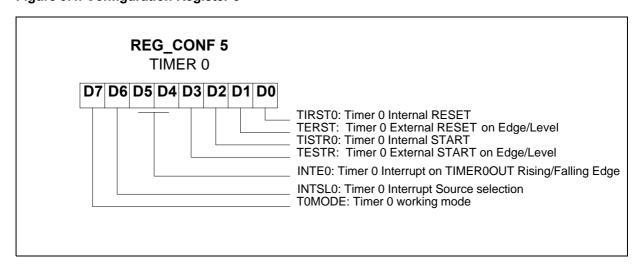

| REG_CONF 5             | PWM/TIMER 0        | PWM/TIMER 0 Working mode Configuration                                |

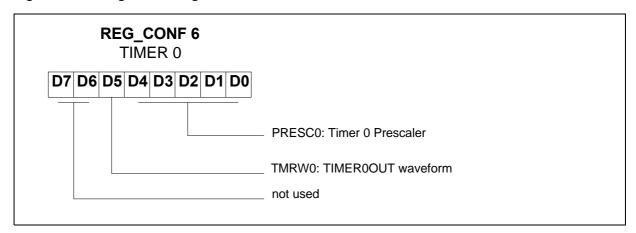

| REG_CONF 6             | PWM/TIMER 0        | PWM/TIMER 0 Prescaler configuration and output waveform selection.    |

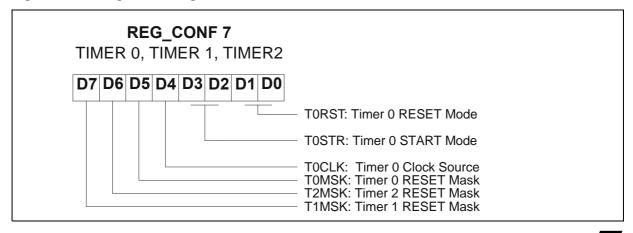

| REG_CONF 7             | PWM/TIMER 0        | PWM/TIMER 0 Working mode Configuration                                |

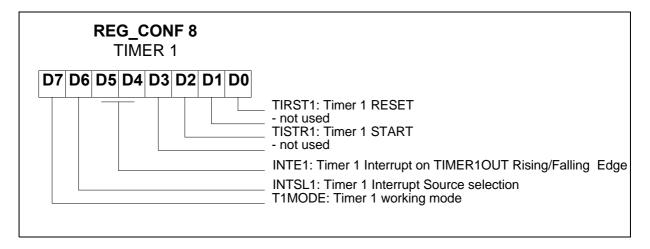

| REG_CONF 8             | PWM/TIMER 1        | PWM/TIMER 1 Working mode Configuration                                |

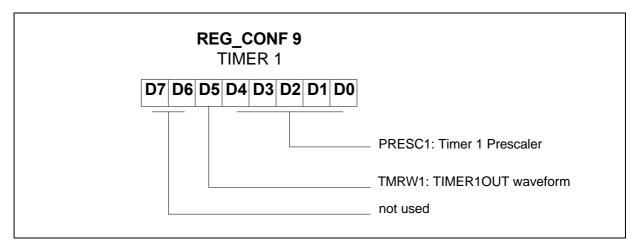

| REG_CONF 9             | PWM/TIMER 1        | PWM/TIMER 1 Prescaler configuration and output waveform selection.    |

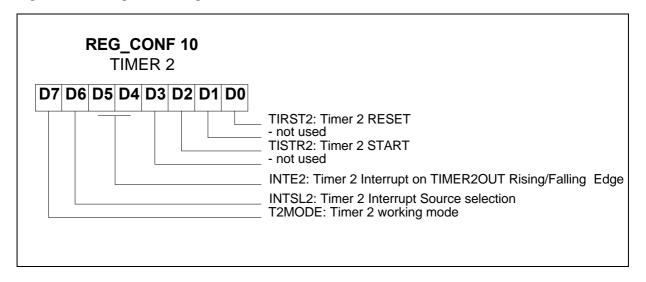

| REG_CONF 10            | PWM/TIMER 2        | PWM/TIMER 2 Working mode Configuration                                |

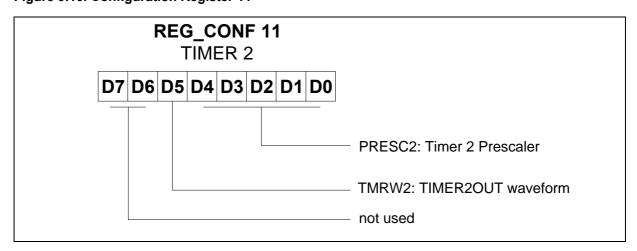

| REG_CONF 11            | PWM/TIMER 2        | PWM/TIMER 2 Prescaler configuration and output waveform selection.    |

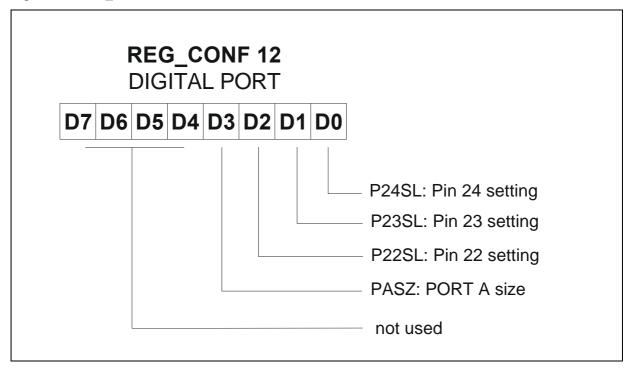

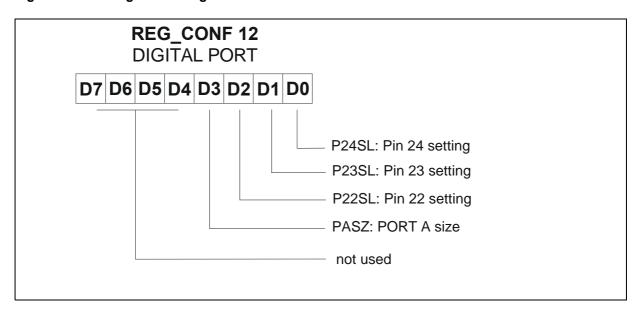

| REG_CONF 12            | PORT A             | Set the bit 0,1 and 2 like Digital I/O o complementary Timers Output. |

| REG_CONF 13            | PORT B             | Set the relative bit like digital input o digital output.             |

| REG_CONF 14            | PORT B             | Set the relative I/O like Digital or<br>Analog                        |

| REG_CONF 15            | PORT C             | Set the relative I/O like digital input of digital output             |

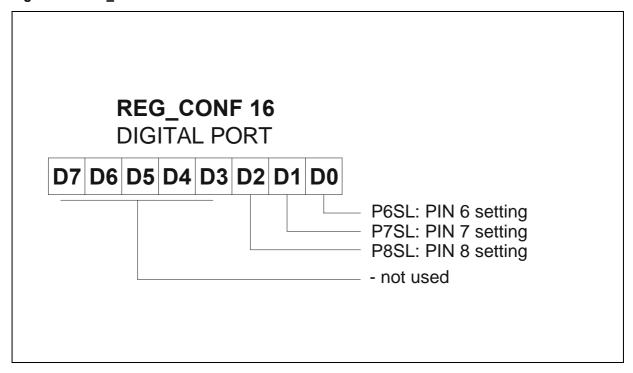

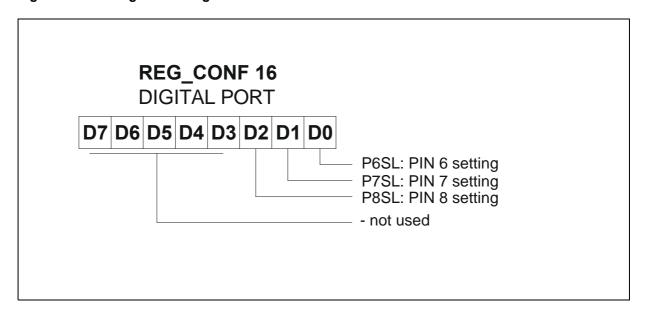

| REG_CONF 16            | PORT C             | Set the relative I/O like Digital I/O or<br>Timers Output             |

Use and meaning of each register will be described in further details in the corresponding section.

2.2.4 Output Registers

The Output Registers (OR) consist of 9 registers containing data for the microcontroller peripherals including the I/O Ports.

All the registers can be specified by using a decimal address, e.g. 1 identifies the second OR.

By using the LOAD instructions it is possible to set the Output Registers (OR) by using values stored in the Program Memory (LDPE) or in the RAM (LDPR)

The assembler instruction:

LDPR OR\_i RAM\_Reg.

loads the value of the RAM location identified by the address RAM\_Reg in the OR i-th

Table 2.4 describes the OR.

For simplicity reasons a mnemonic name is assigned to the OR. The same name is used in  $FUZZYSTUDIO^{TM}$  4 development tools.

Use and meaning of each register will be described in further details in the corresponding section.

**Table 2.4 Output Registers**

| OR MENMONIC NAME | PERIPHERAL                  | ADDRESS |

|------------------|-----------------------------|---------|

| PORT_A           | PORT A OR                   | 0       |

| PORT_B           | PORT B OR                   | 1       |

| PORT_C           | PORT C OR                   | 2       |

| PWM_O_COUNT      | TIMER/PWM 0 COUNTER         | 3       |

| PWM_0_RELOAD     | TIMER/PWM 0 RELOAD REGISTER | 4       |

| PWM_1_COUNT      | TIMER/PWM 1 COUNTER         | 5       |

| PWM_1_RELOAD     | TIMER/PWM 1 RELOAD REGISTER | 6       |

| PWM_2_COUNT      | TIMER/PWM 2 COUNTER         | 7       |

| PWM_2_RELOAD     | TIMER/PWM 2 RELOAD REGISTER | 8       |

**A**7/

#### 2.3 FUZZY CAPABILITIES

ST52x420 Fuzzy main features are:

- Up to 8 Inputs with 8-bit resolution;

- 1 Kbyte of Program Memory (EPROM) available to store more than 300 to Membership Functions (MFs) for each Input;

- Up to 128 Outputs with 8-bit resolution;

- Possibility to process fuzzy rules with an high number of antecedents

- High number of Rules and Fuzzy Blocks.

The limits on the number of Fuzzy Rules and Fuzzy Blocks are only related with the program memory size

#### 2.3.1 Fuzzy Inference

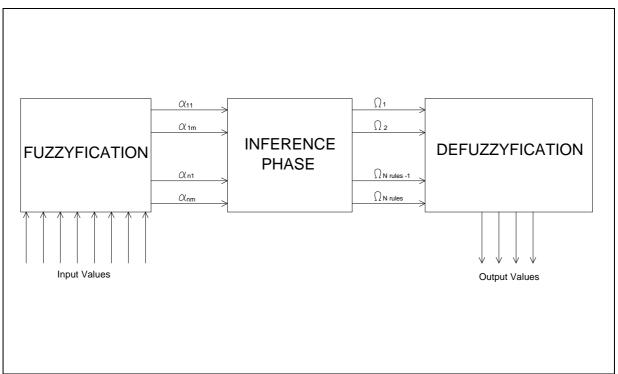

The block diagram shown in figure 2.8 describes the different steps performed during a fuzzy algorithm. ST52x420 Core allows to implement a MAMDANI type fuzzy inference with crisp consequents. The input for the fuzzy inference are stored in 8 dedicated Fuzzy input registers. The instruction LDFR is used to set the input fuzzy registers with the values stored in the RAM.

The result of a fuzzy inference is directly stored in a location of the RAM

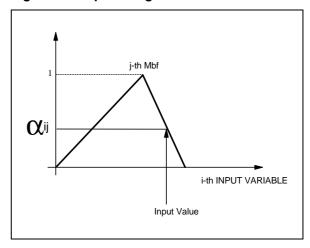

Figure 2.7. Alpha Weigth calculation

# 2.3.2 Fuzzyfication Phase

In this phase is performed the intersection (alpha weight) between the input values and the related MFs (fig. 2.7).

8 Fuzzy input registers are available for the fuzzy inferences.

After loading the input values by using the LDFR assembler instruction, the user can start the fuzzy inference by using the assembrer instruction

Figure 2.8. Fuzzy Inference

FUZZY. During the **fuzzyfication**: the input data are transformed in activation level (alpha weight) of the MFs.

#### 2.3.3 Inference Phase

It manages the alpha weights obtained during the fuzzyfication phase to compute the truth value ( $\omega$ ) for each rule.

This is a calculation of the maximum (for the OR operator) and/or minimum (for the AND operator) performed on alpha values according to the logical connectives of fuzzy rules.

It is possibile to link together several conditions by linguistic connectives AND/OR, NOT operator and brackets.

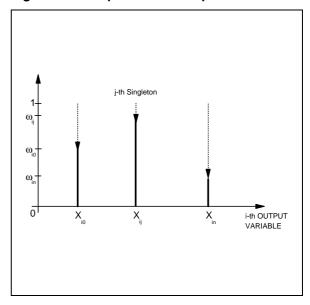

The truth value  $\omega$  and the related output singleton are passed to the Defuzzyfication phase to complete the inference calculation.

# 2.3.4 Defuzzyfication

In this phase the output crisp values are determined implementing the consequent part of the rules.

Each consequent Singleton  $X_i$  is multiplied by its weight values  $\omega_i$ , calculated by the Fuzzy Inference Unit in order to compute the upper part of the defuzzification.

Figure 2.9. Fuzzyfication

Figure 2.10 Output Membership Functions.

Each output value is deduced from the consequent crisp values  $(X_i)$  by using the defuzzification formula:

$$Y_{i} = \frac{\sum_{j}^{N} X_{ij} \omega_{ij}}{\sum_{j}^{N} \omega_{ij}}$$

where:

i = identifies the current output variable

N = number of the active rules on the current output

$\omega_{ii}$  =weigth of the j-th singleton

Xij = abscissa of the j-th singleton

The fuzzy outputs are stored in the RAM location i-th specified in the assembler instruction OUT i.

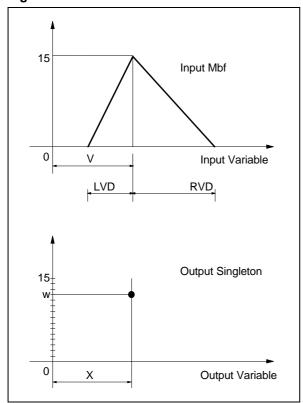

# 2.3.5 Input Membership Function

ST52x420 allows to manage triangular MFs. In order to define a MF it is necessary to store three different data on the program memory:

the vertex of the MF: V;

the length of the left semi-base: LVD; the lenght of the right semi-base: RVD;

In order to reduce the size of the memory area and the computational effort the vertical dimension of the vertex is fixed to 15 (4 bits)

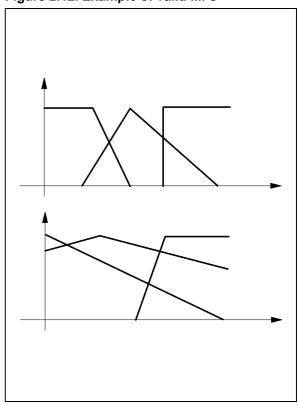

By using the previous memorization method it is possible to store different kinds of triangular Membership Functions. The figure 2.12 shows a typical example of MFs that can be defined in ŠT52x420.

Each MF is then defined storing 3 bytes in the first 1 Kbyte of the memory program.

The MF is memorized by using the following instruction:

MF n MF lvd v rvd

n\_MF identifies the MF, Ivd, v, rvd are the parameters describing the MF's shape. In a trapezoidal MF LVD, or RVD, is 0.

## 2.3.6 Output Singleton

ST52x420 uses for the output variables a particular kind of membership function called Singleton. A Singleton has not a shape, like a traditional MF, and it is characterized by a single point identified by the couple  $(X, \omega)$ , where the  $\omega$  is calculated by the Inference Unit as described before.

Often, a Singleton is simply identified with its Crisp Value X.

where

Figure 2.11. MFs Parameters

Figure 2.12. Example of valid MFs

**\_\_\_\_\_** 18/120

# 2.3.7 Fuzzy Rules.

The rules can have the following structures: if A op B op C.....then Z if (A op B) op ( C op D op E...) .....then Z where op is one of the possible linguistic operators (AND/OR)

In the first case the rule operators are managed sequentially; in the second one, the priority of the operator is fixed by the brackets.

Each rule is codified by using an instruction set, the inference time for a rule with 4 antecedents and 1 consequent is about 3 microseconds.

The assembler Instruction Set allowing to manage the fuzzy instructions is reported in the following table

**Table 2.5. Fuzzy Instructions Set**

| Instruction        | Description                                                                                                  |

|--------------------|--------------------------------------------------------------------------------------------------------------|

| MBF n_MF lvd v rvd | Stores the MF n_MF with the shape identified by the parameters lvd, v and rvd.                               |

| LDP n m            | Fixes the alpha value of the input n with the MF m and stores it in internal registers.                      |

| LDN n m            | Calculates the negated alpha value of the input n with the MF m and stores the result in internal registers. |

| FZAND              | Implements the fuzzy operation AND between the last two values stored in internal registers.                 |

| FZOR               | Implements the fuzzy operation OR between the last two values stored in internal registers.                  |

| LDK                | Stores the result of the last fuzzy operation executed in the data stack.                                    |

| SKM                | Stores the result of the last fuzzy operation executed in internal registers.                                |

| LDM                | Copies the value of the register M in the data stack.                                                        |

| CON crisp          | Multiplies the crisp value with the last $\omega$ weight.                                                    |

| OUT n_out          | Performs the defuzzification and store the fuzzy output in the RAM n_out location.                           |

| FUZZY              | Starts the single fuzzy output calculation.                                                                  |

The Assembler instructions operate as in the following example:

Let us suppose you have previously defined the MF with MBF instructions, the rule:

IF Inp0 is NOT MF01 AND Inp2 is MF21 OR Inp3 is MF33 THEN CRISP1

is therefore codified as:

**LDN 0 1** Loads in the stack the NOT value relative to the first term of the rule (supposing

that MF\_num for MF01 is 1).

LDP 2 21 Loads in the stack the value relative to the second term of the rule(supposing that

MF\_num for MF21 is 21).

**FZAND** Calculates the min between two values in the stack. **LDK** Stores the result of the previous operation in the stack.

LDP 3 33 Loads in the stack the value relative to the third term of the rule (supposing that

MF\_num for MF33 is 33).

**FZOR** Calculates the max between the two values in the stack.

**CON 58** Performs the product between the values calculated and the value CRISP1 = 58

(consequent calculus)

Let us suppose now you have the following rule:

IF (Inp2 is MF21 AND Inp3 is NOT MF35) OR (Inp0 is MF03 OR Inp1 is NOT MF16) THEN CRISP2 It is codified with the following instructions:

LDP 2 21 Loads in the stack the value relative to the first term of the rule (supposing that

MF\_num for MF21 is 21).

Loads in the stack the NOT value relative to the second term of the rule (supposing

that MF num for MF35 is 35).

**FZAND** Calculates the min between the two values in the stack. **SKM** Stores the calculated value on the temporary register.

LDP 0 3 Loads in the stack the value relative to the third term of the rule (supposing that

MF\_num for MF03 is 3).

LDN 1 16 Loads in the stack the NOT value relative to the fourth term of the rule (supposing

that MF\_num for MF16 is 16).

FZOR Calculates the max between the two values in the stack.

LDK Stores the result of the previous operation in the stack.

LDM Copies the content of the temporary register in the stack.

FZOR Calculates the max between the two values in the stack

CON 35 Performs the product between the value calculated and the value CRISP1=35 (Con-

sequent calculus).

After the inference of all the rules relative to an output, you can obtain the output through the instruction:

**OUT 0** To calculate the first fuzzy output.

Table 2.6. Arithmetic & Logic Instructions Set

|          | Load Instructions     |       |        |   |   |   |  |

|----------|-----------------------|-------|--------|---|---|---|--|

| Mnemonic | Instruction           | Bytes | Cycles | Z | S | С |  |

| LDCE     | LDCE conf, EPROM      | 3     | 17     | - | - | - |  |

| LDCR     | LDCR conf, RAM        | 3     | 14     | - | - | - |  |

| LDFR     | LDFR FUZZY_i, RAM     | 3     | 14     | - | - | - |  |

| LDPE     | LDPE per, EPROM       | 3     | 17     | - | - | - |  |

| LDPR     | LDPR per, RAM         | 3     | 14     | - | - | - |  |

| LDRC     | LDRC RAM, Const       | 3     | 14     | - | - | - |  |

| LDRE     | LDRE RAMi, Eprom      | 3     | 16     | - | - | - |  |

| (LDRE)   | LDRE (RAMi), (EPROMj) | 3     | 18     | - | - | - |  |

| LDRI     | LDRI RAM i, inp_reg   | 3     | 15     | - | - | - |  |

| LDRR     | LDRR RAM i RAM j      | 3     | 16     | - | - | - |  |

| PGSET    | PGSET const           | 2     | 9      | - | - | - |  |

| Arithmetic Instructions |                 |       |        |   |   |   |

|-------------------------|-----------------|-------|--------|---|---|---|

| Mnemonic                | Instruction     | Bytes | Cycles | z | s | С |

| ADD                     | ADD regi, regj  | 3     | 17     | I | - | I |

| ADDO                    | ADDO regi, regj | 3     | 20     | I | I | I |

| AND                     | AND regi, regj  | 3     | 17     |   | - | - |

| ASL                     | ASL regi        | 2     | 15     | I | - | I |

| ASR                     | ASR regi        | 2     | 15     | - | I | I |

| DEC                     | DEC regi        | 2     | 15     | I | I | - |

| DIV                     | DIV regi, regj  | 3     | 26     | I | I | I |

| INC                     | INC regi        | 2     | 15     | I | - | I |

| MULT                    | MULT regi, regj | 3     | 19     | ı | - | - |

| NOT                     | NOT regi        | 2     | 15     | I | - | - |

| OR                      | OR regi, regj   | 3     | 17     | I | - | - |

| SUB                     | SUB regi, regj  | 3     | 17     | I | I | - |

| SUBO                    | SUBO regi, regj | 3     | 20     | I | I | I |

| MIRROR                  | MIRROR regi     | 2     | 15     | I | - | - |

Table 2.7. Arithmetic & Logic Instructions Set (Continue)

|          |             | Jump Instructions | <b>;</b> |   |   |   |

|----------|-------------|-------------------|----------|---|---|---|

| Mnemonic | Instruction | Bytes             | Cycles   | z | s | С |

| CALL     | CALL addr   | 3                 | 18       | - | - | - |

| JP       | JP addr     | 3                 | 12       | - | - | - |

| JPC      | JPC addr    | 3                 | 10/12    | - | - | - |

| JPNC     | JPNC addr   | 3                 | 10/12    | - | - | - |

| JPNS     | JPNS addr   | 3                 | 10/12    | - | - | - |

| JPNZ     | JPNZ addr   | 3                 | 10/12    | - | - | - |

| JPS      | JPS addr    | 3                 | 10/12    | - | - | - |

| JPZ      | JPZ addr    | 3                 | 10/12    | - | - | - |

| RET      | RET         | 1                 | 13       | - | - | - |

| Interrupt Instructions Set |             |       |        |   |   |   |

|----------------------------|-------------|-------|--------|---|---|---|

| Mnemonic                   | Instruction | Bytes | Cycles | z | S | ပ |

| HALT                       | HALT        | 1     | 7/16   | - | - | - |

| MEGI                       | MEGI        | 1     | 7/16   | - | - | 1 |

| MDGI                       | MDGI        | 1     | 7/16   | - | - | - |

| RETI                       | RETI        | 1     | 12     | - | - | ı |

| RINT                       | RINT INT    | 2     | 8      | - | - | ı |

| UDGI                       | UDGI        | 1     | 7/16   | - | - | i |

| UEGI                       | UEGI        | 1     | 7/16   | - | - | i |

| WAITI                      | WAITI       | 1     | 7      | - | - | - |

| Control instructions set |             |       |        |   |   |   |

|--------------------------|-------------|-------|--------|---|---|---|

| Mnemonic                 | Instruction | Bytes | Cycles | z | s | С |

| FUZZY                    | FUZZY       | 1     | 5      | - | • | • |

| NOP                      | NOP         | 1     | 6      | - | ı | ı |

| WDTRFR                   | WDTRFR      | 1     | 7      | - |   |   |

| WDTSLP                   | WDTSLP      | 1     | 6      | - | - | - |

Notes: I affected, IS stacked value restored, - not affected

#### 2.4 ARITHMETIC LOGIC UNIT

The 8-bit Arithmetic Logic Unit (ALU) allows to perform arithmetic calculations and logic instructions which can be divided into 5 groups: Load, Arithmetic, Jump, Interrupts and Program Control instructions (refer to the ST52x420 Assembler Set for further details).

The computational time required for each instruction consists of one clock pulse for each Cycle plus 3 clock pulses for the decoding phase.

The ALU of the ST52x420 is able to perform multiplication (MULT) and division (DIV), by means of an hardware multiplier and an hardware divider. In this way it is possible to increase the computational throughput and reduce code size requirement for complex algorithms. The multiplication is performed by using 8 bit operands storing the result in 2 registers (16 bit values), see Figure 2.13. The division is performed between a 16 bit dividend and an 8 bit divider, the result is stored in an 8 bit register (See Fig. 2.14)

#### 2.5 ST52x420 Assembler Pseudo Instructions

The ST52x420 assembler instructions set includes some pseudo instructions.

The Assembler pseudo instructions are used to set the data for the Fuzzy Computation, the Assembler then optimizes these data considering the code format used from the Fuzzy Computation Unit.

The Assembler pseudo instructions have not direct correspondence with the machine code; this is obtained after the elaboration of the supplied data by means of the Assembler.

There are also the pseudo instructions to set data and to set the current location in EPROM Memory.

For more details see the chapter related to the instructions set.

Figure 2.13 Multiplication

Figure 2.14 Division

**A7/**

#### 3 EPROM

The EPROM memory provides an on-chip user-programmable non-volatile memory, that allows fast and reliable storage of user data.

The EPROM memory can be locked by user. In fact a memory location, called Lock Cell, is devoted to lock the EPROM and to avoid external operations. It is possible to write a software identification code, called ID CODE, to distinguish which software version is stored in the memory.

There are 32 kbits of memory space with an 8-bit internal parallelism (4 kbytes) addressed by an 12-bit bus. The data bus is of 8 bits.

The memory has a double supply: V<sub>PP</sub> is equal to 12V±5% in Programming Phase or to V<sub>SS</sub> during Working Phase. V<sub>DD</sub> is equal to 5V±10%.

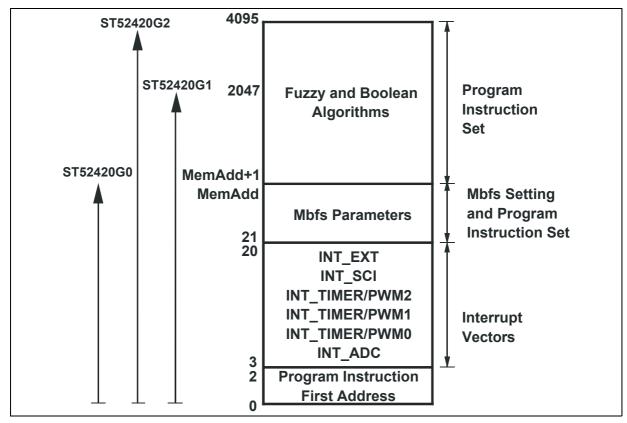

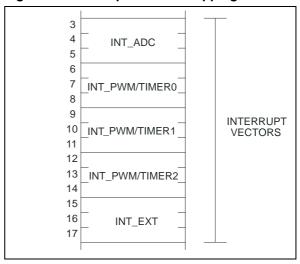

The ST52x420 EPROM memory is divided into three main blocks (see Figure 3.1):

- Interrupt Vectors memory block (3 through 17) contains the jump instructions to the addresses for the interrupt routines. Each interrupt vector is composed of three bytes.

- Mbfs Setting memory block (18 through 1023) contains the coordinates of the vertexes of every

Mbf defined in the program. The memory space of this block, not used to contain the Mbfs settings, is available for the Program instructions set

■ The Program Instruction Set memory block (1024 through 4095) contains the instruction set of the user program.

The locations 0, 1 and 2 contain the address of the first microcode instruction.

The operations that can be performed on the EPROM during the Programming Phase are: Stand By, Memory Writing, Reading and Verify, Memory Lock, IDCode Writing and Verify.

Above operations are managed by using an internal 4-bit configuration register and an EPROM Configuration Register. Depending on the value written in such register, the corresponding operation is performed. The reading phase is executed with  $V_{PP}=5V\pm5\%$ , while the verify phase needs  $V_{PP}=12V\pm5\%$ . The Blank Check must be a reading operation with  $V_{PP}=5V\pm5\%$ .

Table 3.1 shows the EPROM Configuration Register codes used to identify the running operation.

Figure 3.1. Memory Map

# 3.1 EPROM Programming Phase Procedure

The Programming mode is selected by applying 12V±5% voltage or 5V±5% voltage to the V<sub>PP</sub> pin and setting the control signal as follows:

RESET (pin 1) =Vss

TEST (pin 4) =Vss

If the  $V_{\text{PP}}$  voltage is  $5V\pm5\%$  it is possible only to read.

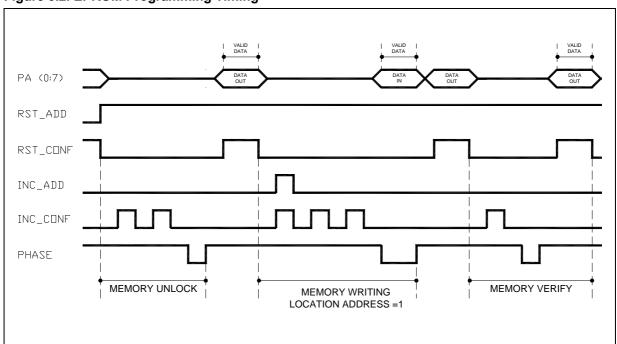

RST\_ADD (pin 9), INC\_ADD (pin 10), RST\_CONF (pin 11), INC\_CONF (pin 12) and PHASE (pin 5) are the control signals used during the Programming Mode.

PHASE,RST\_CONF and RST\_ADD signals are active on level, the others are active on rising edge.

PHASE and RST\_ADD signals are active low, RST\_CONF signal is active high.

Data in/out digital port is PORT A (from pin 18 up to pin 25).

It is possible to lock the memory by means of the Memory Lock Status, that is a flag used to enable the EPROM operations.

If Memory Lock Status is 1 all EPROM operations are enabled, otherwise, it is only possible to read (and verify) the OTP code and the Memory Lock Status.

Only If the EPROM is not locked by means of Lock Cell (see paragraph 3.1.2), it is possible to enable the EPROM operations, changing the Memory Lock Status from 0 to 1.

**RST\_ADD** signal resets the memory address register and the Memory Lock Status. For this reason, when the RST\_ADD becomes high, it is necessary to unlock the memory to read or write.

**INC\_ADD** signal increments the memory address register value, that is the address of the EPROM memory cell that will be affected by the operation in progress.

**RST\_CONF** signal resets the EPROM Configuration Register. When RST\_CONF is high, the DATA I/O Port A is in output, otherwise it is always in input.

**INC\_CONF** signal increments the EPROM Configuration Register value.

**PHASE** signal validates the operation selected by means of EPROM Configuration Register value. When PHASE signal is low valid data have to be present in the PORT A.

#### 3.1.1 EPROM Operation

To execute one EPROM operation, the corresponding identification value must be loaded in the EPROM Configuration Register (see table 3.1). The signal timing is the following:

- -- RST ADD= high and PHASE= high,

- a positive pulse on RST\_CONF signal reset the EPROM Configuration Register,

- INC\_CONF signal generates a number of positive pulses equal to the value to be loaded in the EPROM Configuration Register.

- After this sequence, a negative pulse of the PHASE signal will validate the selected operation. During Writing operations valid data have to be present in the Port A when PHASE signal is low.

The minimum PHASE signal pulse width must be 10 µs for the EPROM Writing Operation and 100 ns for the others.

If the EPROM Configuration Register has not been reseted, every INC\_CONF signal impulse increases the existing value.

When RST\_CONF is high, the DATA I/O PORT A is enabled in output and the reading / verify operation results are available.

After a writing operation, when RST\_CONF is high, the Port A is in output with no valid data.

**Table 3.1. EPROM Configuration Register**

| OPERATION                                | REGISTER VALUE |

|------------------------------------------|----------------|

| Stand By                                 | 0              |

| Memory<br>Reading / Verify               | 1              |

| Memory Unlock and Lock<br>Status Reading | 2              |

| Memory<br>Writing                        | 3              |

| Memory<br>Lock                           | 4              |

| ID CODE<br>Writing                       | 5              |

| Memory Lock Status<br>Reading / Verify   | 9              |

| ID CODE<br>Reading / Verify              | 10             |

# 3.1.2 EPROM Locking

The Memory Lock operation, that is identified with the number 4 in the EPROM Configuration Register, writes "0" in the Memory Lock Cell.

At the beginning of an External Operation, when RST\_ADD signal changes from low level to high level, the Memory Lock Status is "0", therefore it is necessary to unlock it before to proceed.

To unlock the Memory Lock Status the operation, that is identified with the number 2 in the EPROM Configuration Register must be executed (see Figure 3.2).

The Memory Lock Status can be changed only if Memory Lock Cell is "1", therefore, for this reason, after a Memory Lock operation it is not possible to execute external operations except to read (or verify) the OTP Code and the Memory Lock Status

# 3.1.3 EPROM Writing

When the memory is blank, all the bits are at logic level "1". The data are introduced by programming only the zeros in the desired memory location; however all input data must contain both "1" and "0".

The only way to change "0" into "1" is to erase the whole memory (by exposure to Ultra Violet light) and reprogram it.

The memory is in Writing mode when the EPROM Configuration Register value is 3 (see table 3.1).

The  $V_{PP}$  voltage must be 12V±5%, with stable data on the data bus PA(0:7).

The signals timing is the following (see Figure 3.2):

- 1) RST\_ADD and RST\_CONF change from low to high level,

- 2) two pulses on INC\_CONF signal load the Memory Unlock operation code,

- 3) a negative pulse (100 ns) on the PHASE signal validates the Memory Unlock operation,

- 4) a negative pulse on RST\_CONF signal resets the EPROM Configuration Register,

- 5) three positive pulses on INC\_CONF load the Memory Writing operation code (see table 3.1),

- 6) a train of positive pulses on INC\_ADD signal increments the memory location address up to the requested value (generally this is a sequential operation and only one pulse is used),

- 7) valid data have to be present in the PORT A (this step can be performed before),

- 8) a negative pulse (10  $\mu$ s) on the PHASE signal validates the Memory Writing operation and the memory location is written.

For sequential Writing operations, it is necessary to repeat the steps since 6 to 7.

#### 3.1.4 EPROM Reading / Verify

The reading phase is executed with V<sub>PP</sub>= 5V±5%, instead of verify phase that needs V<sub>PP</sub>= 12V±5%.

The Memory Verify operation is available in order to verify the correctness of the data written. It is possible to execute a Memory Verify operation immediately after the writing of each byte and in this case (see Figure 3.2):

- 1) a positive pulse on RST\_CONF signal resets the EPROM Configuration Register, if it was not already reseted

- 2) one positive pulse on INC\_CONF loads the Memory Reading/Verify operation code,

- 3) a negative pulse (100 ns) on the PHASE signal validates the Memory Reading / Verify operation,

- 4) a negative pulse on RST\_CONF signal puts in the PA(0:7) pins (Port A) the value stored in the actual memory address and resets the EPROM Configuration Register.

Then, if any error in writing occured, the user has to repeat the EPROM writing.

# 3.1.5 Stand by Mode

The EPROM has a standby mode which reduces the active current from 10 mA (Programming mode) to less than 100  $\mu$ A. The Memory is placed in standby mode by setting PHASE signal at high level or when the EPROM Configuration register value is 0 and PHASE signal is low.

#### 3.1.6 ID code

It is possible to write a software identification code, called ID code, to distinguish which software version is stored in the memory.

64 Bytes are dedicated to store this code by using the address values from 0 to 63.

It is possible to read or verify the ID Code also if the Memory Lock Status is "0".

The signals timing is the same of a normal operation (see paragraph 3.1.1).

#### 3.2 Eprom Erasure

Thanks to the transparent window available in the CDIP28W package, its memory contents may be erased by exposure to UV light.

Erasure begins when the device is exposed to light with a wavelength shorter than 4000Å. It should be noted that sunlight, as well as some types of artificial light, includes wavelengths in the 3000-4000Å range which, on prolonged exposure, can cause erasure of memory contents. It is thus recommended that EPROM devices be fitted with

an opaque label over the window area in order to prevent unintentional erasure.

The recommended erasure procedure for EPROM devices consists of exposure to short wave UV light having a wavelength of 2537Å. The minimum recommended integrated dose (intensity x expo-sure time) for complete erasure is 15Wsec/cm 2.

This is equivalent to an erasure time of 15-20 minutes using a UV source having an intensity of 12mW/cm 2 at a distance of 25mm (1 inch) from the device window.

#### **4 INTERRUPTS**

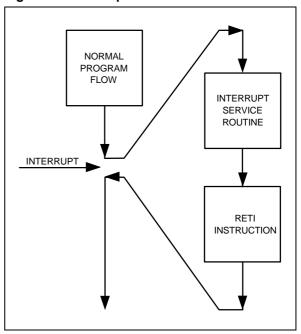

The Control Unit (CU) responds to peripheral events and external events through its interrupt channels.

When such an event occurs, if the related interrupt is not masked and according to a priority order, the current program execution can be suspended to allow the CU to execute a specific response routine.

Each interrupt is associated with an interrupt vector that contains the memory address of the related interrupt service routine. Each vector is located in the Program Space (EPROM Memory) at a fixed address (see Interrupt Vectors table fig. 4.2).

# **4.1 Interrupt Functionment**

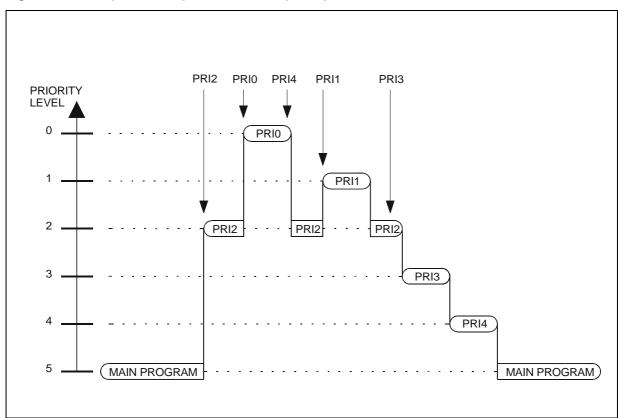

If, at the end of an arithmetic or logic instruction, there are pending interrupts, the one with the highest priority is passed. To pass an interrupt means to store the arithmetic flags and the current PC in the stack and execute the associated Interrupt routine, whose address is located in two bytes of the EPROM memory location between address 2 and 17.

The Interrupt routine is performed as a normal code checking, at the end of each instruction, if an higher priority interrupt has to be passed. An Interrupt request with the higher priority stops the lower priority Interrupt. The Program Counter and the arithmetic flags are stored in the stack.

With the instruction RETI (Return from Interrupt) the arithmetic flags and Program Counter (PC) are restored from the top of the stack. This stack was already described in the section 2.2.1.

An Interrupt request cannot stop the processing of the fuzzy rules, but this is passed only after the end of a fuzzy rule or at the end of a logic, or arithmetic, instruction.

REMARK: A Fuzzy routine can be interrupted only in the main program. An interrupt request doesn't have to stop a Fuzzy function, that is running in another interrupt routine. For this reason, to use a fuzzy function inside an interrupt routine, the user has to include the fuzzy function between an UDGI (MDGI) instruction and an UEGI (MEGI) instruction (see the following paragraphs), in order to disable the interrupt request during the execution of the fuzzy function.

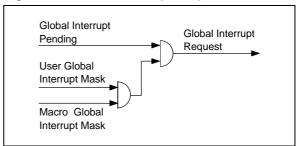

# 4.2 Global Interrupt Request Enabling

When an Interrupt occurs, it generates a Global Interrupt Pending (GIP), that can be hanged up by software. After a GIP a Global Interrupt Request (GIR) will be generated and Interrupt Service

Figure 4.1. Interrupt Flow

Figure 4.2. Interrupt Vectors Mapping

Figure 4.3. Global Interrupt Request

Routine associated to the interrupt with higher priority will start.

In order to avoid possible conflicts between interrupt masking set in the main program, or inside macros, the GIP is hanged up through the User Global Interrupt Mask or the Macro Global Interrupt Mask (see fig.4.3).

UEGI/UDGI instruction switches on/off the User Global Interrupt Mask enabling/disabling the GIR for the main program.

MEGI/MDGI instructions switches on/off the Macro Global Interrupt Mask in order to ensure that the macro will not be broken.

# 4.3 Interrupt Sources

ST52x420 manages interrupt signals generated by the internal peripherals (PWM/Timers and Analog to Digital Converter) or coming from the INT/PC0 pin. The External Interrupt is active on high level of INT/PC0 signal.

Each peripheral can be programmed in order to generate the associated interrupt; further details are described in the related chapter.

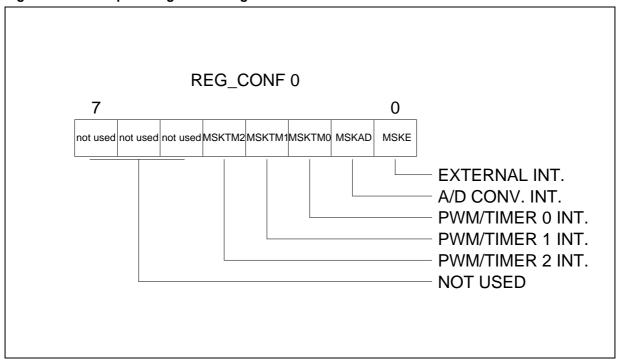

# 4.4 Interrupt Maskability

The interrupts can be masked by configuring the REG\_CONF 0 by means of LDCR, or LDCE, instruction. The interrupt is enabled when the bit associated to the mask interrupt is "1". Viceversa, when the bit is "0", the interrupt is masked and is kept pendent.

# For example:

LDRC 10,6 //loads the constant 6 in the RAM Register 10  $\,$

LDCR 0, 10 // sets the CONF\_REG 0 with the value stored in the RAM Register 10

the result is CONF\_REGO =00000110 thus enabling the interrupts coming from the ADC

Table 4.1. Configuration Register 0

| Bit      | Name       | Value | Description                           |

|----------|------------|-------|---------------------------------------|

| 0        | MSKE       | 0     | External Interrupt<br>Masked          |

|          |            | 1     | External Interrupt<br>Not Masked      |

| 1        | MSKAD      | 0     | A/D Converter Interrupt<br>Masked     |

| 1        | MSKAD      | 1     | A/D Converter Interrupt<br>Not Masked |

| 2        | MSKTM0     | 0     | PWM/TIMER 0 Interrupt<br>Masked       |

| 2 MSKTM0 | IVISKTIVIO | 1     | PWM/TIMER 0 Interrupt<br>Not Masked   |

| 3        | MSKTM1     | 0     | PWM/TIMER 1 Interrupt<br>Masked       |

| 3 MSKIM  | MINING     | 1     | PWM/TIMER 1 Interrupt<br>Not Masked   |

| 4        | MOZTMO     | 0     | PWM/TIMER 2 Interrupt<br>Masked       |

| 4 MSKTM  |            | 1     | PWM/TIMER 2 Interrupt<br>Not Masked   |

| 5        | not used   | -     |                                       |

| 6        | not used   | -     |                                       |

| 7        | not used   | 0     |                                       |

| ,        |            | 1     |                                       |

Reset Configuration '00000'

**Table 4.2. Interrupts Description**

| Name           | Description              |     | Priority     | Peripheral<br>Code | Maskable | EPROM<br>Locations |

|----------------|--------------------------|-----|--------------|--------------------|----------|--------------------|

| INT_ADC        | ADC                      | Int | Programmable | 00                 | yes      | 3-5                |

| INT_PWM/TIMER0 | PWM/TIMER 0              | Int | Programmable | 01                 | yes      | 6-8                |

| INT_PWM/TIMER1 | PWM/TIMER 1              | Int | Programmable | 10                 | yes      | 9-11               |

| INT_PWM/TIMER2 | PWM/TIMER 2              | Int | Programmable | 11                 | yes      | 12-14              |

| INT_EXT        | External Interrupt (INT) | Ext | Highest      | -                  | yes      | 15-17              |

477

Figure 4.4. Interrupt Configuration Register 0

Figure 4.5. Interrupt Configuration Register 1

(INT\_ADC) and from the PWM/TIMER 0 (INT\_PWM/TIMER0).

# 4.5 Interrupt Priority

Six priority levels are available: level 5 has the lowest priority, level 0 has the highest priority.

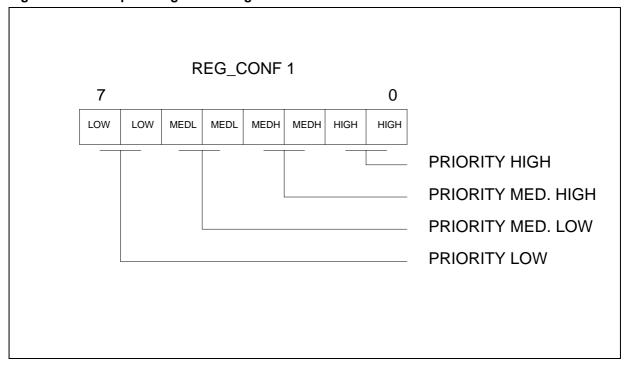

Level 5 is associated to the Main Program, levels 4 to 1 are programmable by means of the priority register called REG\_CONF1 (see fig.4.5 and table 4.3); whereas the higher level is related to the external interrupt (INT\_EXT).

PWM/Timers and ADC are identified by a two-bits Peripheral Code (see Table 4.2); in order to set the *i*-th priority level the user must write the peripheral label *i* in the related PRI*i* priority level.

i.e.

LDRC 10, 201 //(loads the value 201='11001001' in the RAM Register 10)

LDCR 1, 10 // sets the REG\_CONF1= '11001001'

thus defining the following priority levels:

**Table 4.3. Configuration Register 1**

| Bit  | Name | Value              | Priority Level |

|------|------|--------------------|----------------|

| 0, 1 | PRI1 | Peripheral<br>Code | High           |

| 2, 3 | PRI2 | Peripheral<br>Code | Medium-High    |

| 4, 5 | PRI3 | Peripheral<br>Code | Medium-Low     |

- Level 1: INT\_PWM/TIMER0(PWM/TIMER 0 Code: 01)

- Level 2: INT\_PWM/TIMER0(PWM/TIMER 1 Code: 10)

- Level 3: INT\_ADC(ADC Code: 00)

- Level 4: INT\_PWM/TIMER0(PWM/TIMER 2 Code: 11)

REMARK: the Interrupt priority must be fixed ad the beginning of the main program, because at the RESET REG\_CONF1='00000000', and this

Figure 4.6. Example of a Sequence of Interrupt Requests

condition could generate wrong operations. During the program execution it is possible to modify the interrupt priority only with the following procedure:

step 1):

mask the interrupts by means of a UDGI (or MDGI) instruction

step 2):

change the REG\_CONF1 value to modify the interrupt priority

step 3):

reset by mean of RINT instructions all the pending interrupt routines

step 4):

unmask the interrupts by mean of a UEGI (or MEGI) instruction

When a source provides an Interrupt request, and the request processing is also enabled, the CU changes the normal sequential flow of a program by transferring program control to a selected service routine.

When an interrupt occurs the CU executes a JUMP instruction to the address loaded in the related location of the Interrupt Vector.

When the execution returns to the original program, it begins immediately following the interrupted instruction.

REMARK: when an interrupt is masked, it is excluded from the priority arbitration. This may cause the following side-effect: if an interrupt is masked during the servicing of his own service routine, this may be interrupted by lower priority sources. To avoid any problem you can mask the interrupt just at the end of the routine.

# 4.6 Interrupts and Low power mode

All not masked interrupts allow the processor to leave the WAIT low power mode. External interrupt and ext. RESET allow the processor to leave the HALT low power mode.

Table 4.4. RINT instruction code

| Name           | Description        | Value |

|----------------|--------------------|-------|

| INT_ADC        | ADC                | 0     |

| INT_PWM/TIMER0 | PWM/TIMER 0        | 1     |

| INT_PWM/TIMER1 | PWM/TIMER 1        | 2     |

| INT_PWM/TIMER2 | PWM/TIMER 2        | 3     |

| INT_EXT        | External Interrupt | 4     |

# 4.7 Interrupt RESET

An eventually pending interrupt can be reset with the instruction RINT j, which resets the interrupt of the peripheral j according to the following table (see table 4.4)

REMARK: RINT command must be preceded from a UDGI (or MDGI) command and followed by a UEGI (or MEGI) command.

# 5 CLOCK, RESET & POWER SAVING MODE 5.1 Clock System

The ST52x420 Clock Generator module generates the internal clock for the internal Control Unit, ALU and on-chip peripherals and it is designed to require a minimum of external components.

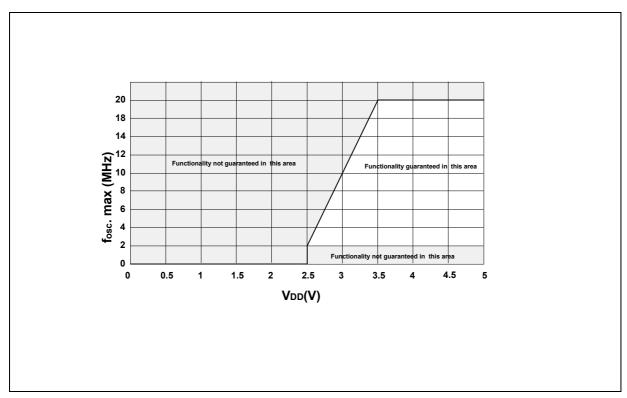

The ST52x420 oscillator circuit generates an internal clock signal with the same period and phase as at the OSCin input pin. The maximum frequency allowed is **20 MHz**.

The system clock may be generated by using either a quartz crystal, or a ceramic resonator (CERALOC); or, at least, by means of an external clock.

The different clock generator options connection methods are shown in Figure 5.1.

When an external clock is used, it must be connected to the pin OSCin, while OSCout must be kept floating.

The crystal oscillator start-up time is a function of many variables: crystal parameters (especially R<sub>S</sub>), oscillator load capacitance (CL), IC parameters, environment temperature, supply voltage.

It must be observed that the crystal or ceramic leads and circuit connections must be as short as

possible. Typical values for CL1, CL2 are 10pF for a 20 MHz crystal.

**Figure 5.1 Oscillator Connections**

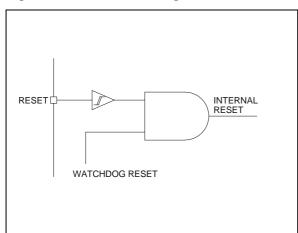

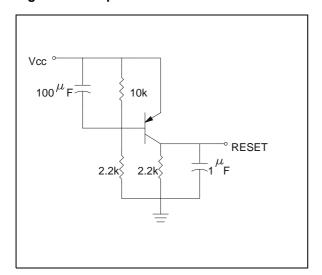

#### 5.2 RESET

There are two sources of Reset:

- RESET pin (external source.)

- WATCHDOG (Internal Source)

When a Reset event happens, the user program restarts from the beginning.

The Reset pin is an input. An internal reset does not affect this pin.

A Reset signal originated by external sources is instantaneously recognised. The RESET pin may be used to ensure  $V_{DD}$  has risen to a point where the MCU can operate correctly before the user program is run. In working mode the Reset must be set to  $V_{DD}$  (see Table 2.1)

Figure 5.2 Reset Block Diagram

Figure 5.4 Simple Reset Circuit

# 5.3 Power Saving Mode

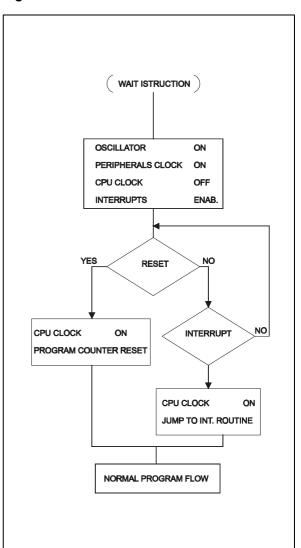

There are two Power Saving modes: WAIT and HALT mode. These conditions may be entered using the WAIT or HALT instructions.

#### 5.3.1 Wait Mode

Wait mode places the MCU in a low power consumption by stopping the CPU. All peripherals remain active. During the WAIT mode, the unmasked Interrupts are enabled. The MCU will remain in Wait mode until an Interrupt or a RESET occurs, whereupon the Program Counter jumps to the interrupt service routine or, if a RESET occurs, at the beginning of the user program.

Figure 5.3 WAIT Flow Chart

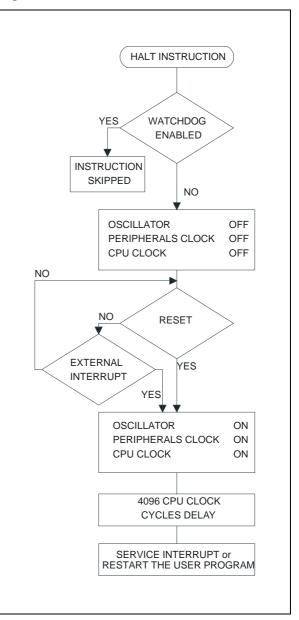

#### 5.3.2 Halt Mode

The Halt mode is the MCU lowest power consumption mode. The Halt mode is entered by executing the HALT instruction. The internal oscillator is turned off, causing all internal processing to be stopped, including the operations of the on-chip peripherals. **The Halt mode cannot be used when the watchdog is enabled**. The HALT instruction will be skipped, if it is executed while the watchdog system is enabled.

In Halt mode the external interrupt is enabled. If an interrupt occurs, the CPU becomes active.

The MCU can exit the Halt mode upon reception of an external interrupt or a reset. The oscillator is then turned on and a stabilisation time is provided before restarting the CPU operations. The stabilisation time is 4096 CPU clock cycles.

#### Wake-Up from HALT mode

After the start up delay, the CPU restarts the operations.

The device can wake up from the HALT mode through one of the following events:

- 1) External Interrupt

- 2) External reset fetching the reset vector

Wake-up is regardless of the state of the External Interrupt mask. If a not masked External Interrupt occurs, the device, after the start up delay, continues executing the External Interrupt service routine. If a masked External Interrupt occurs, the device, after the start up delay, continues executing the User Program.

If the External Reset occurs, the device, after the start up delay, restarts the User Program.

Figure 5.5 HALT Flow Chart

#### 6. I/O PORTS

#### 6.1 Introduction

ST52x420 devices feature flexible individually programmable multifunctional input/output lines. Refer to figures 1.3 and 1.4 for specific pin allocations.

19 I/O lines, grouped in 3 different ports, are available on the ST52x420:

**PORT A =** 7 or 8-bit port (PA0 - PA7 pins)

**PORT B** = 7 or 8-bit port (PB0 - PB7 pins)

PORT C = 4-bit port. (PC0 - PC3 pins)

The PIN 18 can be configured to belong to the port A or to the port B.

These I/O lines can be programmed to provide digital input/output and analog input, or to connect input/output signals to the on chip peripherals as alternate pin functions.

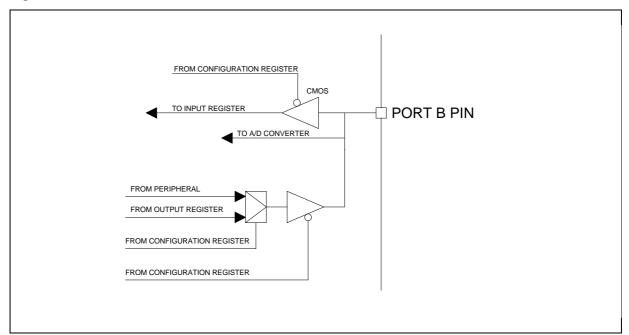

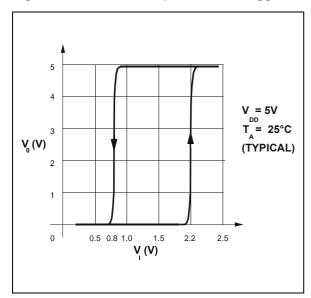

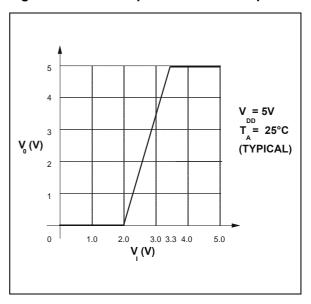

The input buffers are TTL compatible with Schmitt trigger in the port A and C while the port B is CMOS compatible without Schmitt trigger. Refer to chapter 10 for more details.

The output buffer is able to supply up to 8 mA.

The port cannot be configured to be at the same time input and output.

Each port is configured by using two configuration registers. The first is used to define if a pin is an input or output while the second defines the Alternate functions.

REMARK: For a safe use of parallel port as digital I/O, it is recomended to configure the

port B and C with all pins in input or output: you can group all the pins in one direction in the port B and the ones in the opposite direction in the port C. You can fully use the port A pins in both directions. Otherwise, you should operate as follow:

- 1) Reserve two RAM location: one for port B and one for port C.

- 2) When writing on port, first write to the reserved location and then send it to port.

- 3) When reading from port, first write the reserved location to port and then read it, otherwise the output pins may be subject to unwanted modification because the bus content is latched also in reading operation.

Be sure to prevent interrupts between the dummy writing intruction and the reading.

#### Example:

*Idrr 0, 20*; RAM 0 is the reserved location for portB *Idpr 1,0*; write data to port B

udgi; disables interrupt

*Idpr 1,0*; this dummy instruction causes the port B latch to be loaded with the right values of the output pins

*Idri 30,10;* reads data from port B without modifing the output pins

uegi; enables the interrupt

**N.B.:** you can use the port pins in alternate function normally.

Figure 6.1 Ports A & C Functional Blocks

Figure 6.2 Port B Functional Blocks

#### 6.2 Input Mode

The input configuration is selected setting to "1" the corresponding configuration register bit (REG\_CONF 4, 13 and 15) (see paragraph 6.5). The ports are configured by using the configuration registers shown in the following table.

Table 6.1 I/O Port Configuration Registers

| PORT A     | PORT B      | PORT C      |

|------------|-------------|-------------|

| Reg_Conf 4 | Reg_Conf 13 | Reg_Conf 15 |

The digital input data are automatically stored in the Input Registers, but it is not possible to read directly the single bit of the IR and it is necessary to copy the value in a RAM location.

The digital data are stored in a RAM location by using the assembler instruction:

LDRI RAM\_Reg Input\_i

#### 6.3 Output Mode

The output configuration is selected setting to '0' the corresponding configuration register bit (REG\_CONF 4, 13 and 15) (see paragraph 6.5).

The digital data are transferred to the related I/O Port by means of the Output register, by using the assembler instructions LDPE or LDPR.

At RESET the Output Registers are '00000000'.

#### 6.4 Alternate Functions.

Several ST52x420 pins are configurable to be used with different functions (see table 1.1).

When an on chip peripheral is configured to use a pin, it is mandatory to select the correct I/O mode of the related pin.

For example: if the pin 20 (PA5/T0CLK) has to be used like external PWM/Timer0 clock, the Reg\_Conf4(5) bit must be set to '1'.

When the signal is an input of an on-chip peripheral, the related I/O pin has to be configured in Input Mode.

When a pin is used as an A/D Converter input, the related I/O pin is automatically set in tristate. The analog multiplexer (controlled by the A/D configuration Register) switches the analog voltage present on the selected pin to the common analog rail which is connected to the ADC input.

Table 6.2 Input Register and I/O Ports

| PORT A | PORT B | PORT C |

|--------|--------|--------|

| IR 9   | IR 10  | IR 11  |

Table 6.3 Output Register and I/O Ports

| PORT A | PORT B | PORT C |

|--------|--------|--------|

| OR 0   | OR 1   | OR 2   |

It is recommended not to change the voltage level or loading on any port pin while conversion is running. Furthermore it is recommended not to have clocking pins located close to a selected analog pin.

### 6.5 I/O Port Configuration Registers

The I/O mode for each bit of the three ports are selected by using the Configuration Registers 4, 13 and 15 (See Table 6.1) The structure of these registers is shown in the following tables.

Each bit of the configuration registers sets the I/O mode of the related port pin.

Table 6.4 Ports A REG\_CONF 4

| Bit                            | Name | Value | Description                      |  |

|--------------------------------|------|-------|----------------------------------|--|

| 0                              | D0   | 0     | Set the pin 25 in Output<br>Mode |  |

|                                |      | 1     | Set the pin 25 in Input Mode     |  |

| 1                              | D1   | 0     | Set the pin 24 in Output<br>Mode |  |

|                                |      | 1     | Set the pin 24 in Input Mode     |  |

| 2                              | D2   | 0     | Set the pin 23 in Output<br>Mode |  |

|                                |      | 1     | Set the pin 23 in Input Mode     |  |

| 3                              | D3   | 0     | Set the pin 22 in Output<br>Mode |  |

|                                |      | 1     | Set the pin 22 in Input Mode     |  |

| 4                              | D4   | 0     | Set the pin 21 in Output<br>Mode |  |

|                                |      | 1     | Set the pin 21 in Input Mode     |  |

| 5                              | D5   | 0     | Set the pin 20 in Output<br>Mode |  |

|                                |      | 1     | Set the pin 20 in Input Mode     |  |

| 6                              | D6   | 0     | Set the pin 19 in Output<br>Mode |  |

|                                |      | 1     | Set the pin 19 in Input Mode     |  |

| 7                              | D7   | 0     | Set the pin 18 in Output<br>Mode |  |

|                                |      | 1     | Set the pin 18 in Input Mode     |  |

| Reset Configuration '11111111' |      |       |                                  |  |

Table 6.5 Ports B REG\_CONF 13

| Bit                            | Name | Value | Description                      |  |

|--------------------------------|------|-------|----------------------------------|--|

| 0                              | D0   | 0     | Set the pin 9 in Output Mode     |  |

|                                | D0   | 1     | Set the pin 9 in Input Mode      |  |

| 1                              | D1   | 0     | Set the pin 10 in Output<br>Mode |  |

|                                |      | 1     | Set the pin 10 in Input Mode     |  |

| 2                              | D2   | 0     | Set the pin 11 in Output Mode    |  |

|                                | DZ   | 1     | Set the pin 11 in Input Mode     |  |

| 3                              | D3   | 0     | Set the pin 12 in Output<br>Mode |  |

|                                |      | 1     | Set the pin 12 in Input Mode     |  |

| 4                              | 4 D4 | 0     | Set the pin 15 in Output<br>Mode |  |

|                                |      | 1     | Set the pin 15 in Input Mode     |  |

| 5                              | D5   | 0     | Set the pin 16 in Output<br>Mode |  |

|                                |      | 1     | Set the pin 16 in Input Mode     |  |

| 6                              | D6   | 0     | Set the pin 17 in Output<br>Mode |  |

|                                |      | 1     | Set the pin 17 in Input Mode     |  |

| 7                              | 7 D7 | 0     | Set the pin 18 in Output<br>Mode |  |

|                                |      |       | Set the pin 18 in Input Mode     |  |

| Reset Configuration '11111111' |      |       |                                  |  |

### Table 6.6 Port C REG\_CONF 15

| Bit | Name                       | Value | Description                  |  |  |

|-----|----------------------------|-------|------------------------------|--|--|

| 0   | D0                         | 0     | Set the pin 5 in Output Mode |  |  |

|     | Ы                          | 1     | Set the pin 5 in Input Mode  |  |  |

| 1   | D1                         | 0     | Set the pin 6 in Output Mode |  |  |

|     | וט                         | 1     | Set the pin 6 in Input Mode  |  |  |

| 2   | D2                         | 0     | Set the pin 7 in Output Mode |  |  |

|     | DZ                         | 1     | Set the pin 7 in Input Mode  |  |  |

| 3   | D3                         | 0     | Set the pin 8 in Output Mode |  |  |

| 3   | D                          | 1     | Set the pin 8 in Input Mode  |  |  |

| 4   |                            |       |                              |  |  |

| 5   |                            |       | Not Used                     |  |  |

| 6   |                            |       |                              |  |  |

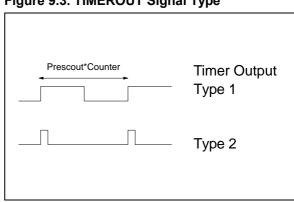

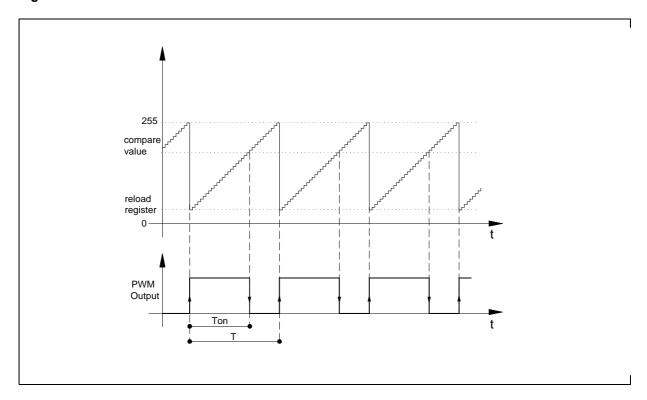

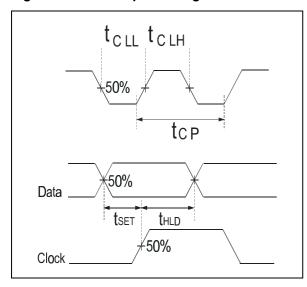

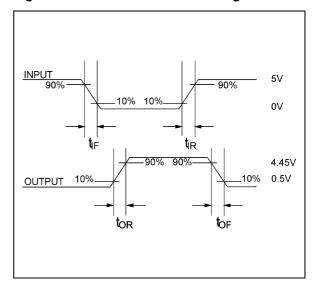

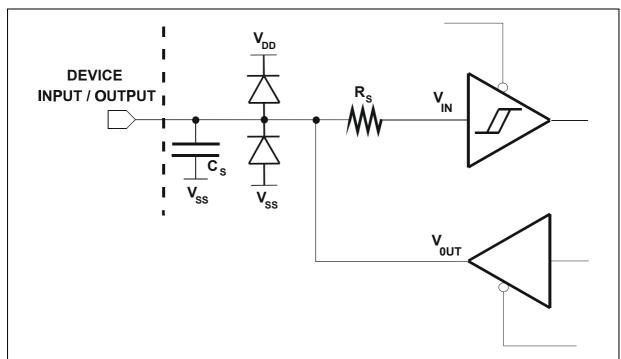

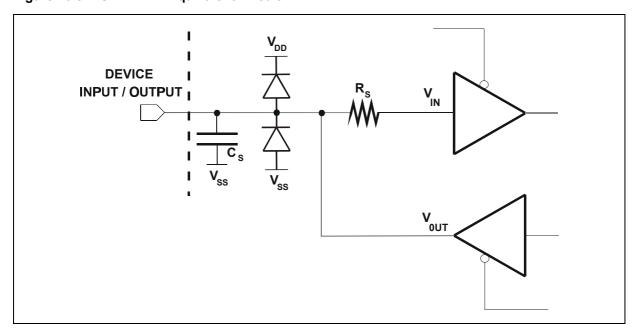

| 7   |                            |       |                              |  |  |